Hardware para cómputo de la imagen integral.

La presente invención, según se expresa en el enunciado de esta memoria descriptiva,

consiste en hardware de señal mixta para cómputo de la imagen integral en el plano focal mediante una agrupación de celdas básicas de sensado-procesamiento cuya interconexión puede ser reconfigurada mediante circuitería periférica que hace posible una implementación muy eficiente de una tarea de procesamiento muy útil en visión artificial como es el cálculo de la imagen integral en escenarios tales como monitorización de espacios naturales, robótica, ayuda a la navegación aérea no tripulada, etc.

El área científico-técnica de la invención es la de tecnologías físicas, concretamente microelectrónica. Su marco de aplicación general sería el de sistemas electrónicos de muy bajo consumo de potencia diseñados para llevar a cabo tareas de visión artificial, es decir, captura de imágenes, análisis de las mismas y actuación en caso de que los resultados de dicho análisis así lo requieran. Como aplicaciones específicas de estos dispositivos se podrían proponer a su vez numerosos ejemplos: monitorización de procesos industriales, monitorización de espacios naturales, vigilancia automatizada de lugares públicos, robótica, ayuda a la navegación aérea no tripulada, etc.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201400224.

Solicitante: UNIVERSIDAD DE SEVILLA.

Nacionalidad solicitante: España.

Inventor/es: RODRIGUEZ VAZQUEZ,ANGEL, CARMONA GALÁN,Ricardo, FERNÁNDEZ BERNI,Jorge, DEL RÍO FERNÁNDEZ,Rocío.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H01L27/00 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › Dispositivos que consisten en una pluralidad de componentes semiconductores o de otros componentes de estado sólido formados en o sobre un sustrato común (detalles H01L 23/00, H01L 29/00 - H01L 51/00; conjuntos que consisten en una pluralidad de dispositivos de estado sólido individuales H01L 25/00).

- H04N5/335 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04N TRANSMISION DE IMAGENES, p. ej. TELEVISION. › H04N 5/00 Detalles de los sistemas de televisión (Detalles de los dispositivos de análisis o sus combinaciones con la producción de la tensión de alimentación H04N 3/00). › que utiliza sensores de imagen de estado sólido [SIES] (H04N 5/32, H04N 5/33 take precedence).

Fragmento de la descripción:

Hardware para cómputo de la imagen integral.

OBJETO DE LA INVENCION

La presente invención, según se expresa en el enunciado de esta memoria descriptiva, consiste en hardware de señal mixta para cómputo de la imagen integral en el plano focal mediante una agrupación de celdas básicas de sensado-procesamiento cuya interconexión puede ser reconfigurada mediante circuitería periférica que hace posible una implementación muy eficiente de una tarea de procesamiento muy útil en visión artificial como es el cálculo de la imagen integral en escenarios tales como monitorización de espacios naturales, robótica, ayuda a la navegación aérea no tripulada etc.

El área científico-técnica de la invención es la de tecnologías físicas, concretamente microelectrónica. Su marco de aplicación general sería el de sistemas electrónicos de muy bajo consumo de potencia diseñados para llevar a cabo tareas de visión artificial, es decir, captura de imágenes, análisis de las mismas y actuación en caso de que los resultados de dicho análisis así lo requieran. Como aplicaciones específicas de estos dispositivos se podrían proponer a su vez numerosos ejemplos: monitorización de procesos industriales, monitorización de espacios naturales, vigilancia automatizada de lugares públicos, robótica, ayuda a la navegación aérea no tripulada etc.

ESTADO DE LA TÉCNICA

El hardware objeto de la presente invención se localizaría físicamente dentro de sistemas empotrados de visión artificial, es decir, sistemas compactos capaces de analizar visualmente una escena de manera autónoma y extraer conclusiones sobre la misma. En concreto, formaría parte del dispositivo fotosensible encargado de capturar las imágenes que son posteriormente procesadas por el resto de elementos del sistema. Este dispositivo, conocido como sensor de imagen, no solo se limitaría a capturar imágenes y, posiblemente, a realizar tareas de mejora de calidad de las mismas-como por ejemplo filtrado de ruido- sino que también podría llevar a cabo el cómputo de las imágenes integrales correspondientes a las imágenes capturadas gracias al hardware propuesto en este documento. Cada pixel de una imagen integral se obtiene como la suma de los pixeles

situados por encima y a la izquierda de ese pixel en la imagen original, de acuerdo a la definición establecida en la especificación industrial OpenVX [OpenVX [Provisional] Specif¡catión, versión 1.0, KhronosGrouDhttDs:// www.khronos.ora/oDenvx . noviembre 2013].

Se podrían citar muchos ejemplos, tanto comerciales como reportados en artículos de investigación, de sensores de imagen "inteligentes" capaces de pre-procesar imágenes como valor añadido a su funcionalidad básica, esto es, captura de imágenes con la mayor calidad posible. Sin embargo, este número se reduce considerablemente cuando el modo de operación de dichos sensores inteligentes se restringe al del hardware objeto de esta invención. Hablamos de una operación basada en una agrupación matricial de celdas básicas de sensado-procesamiento interconectadas entre sí dentro de un circuito integrado, también comúnmente conocido como chip. Estas celdas explotan el uso de circuitería de señal mixta para llevar a cabo, de forma masivamente paralela, determinadas tareas de bajo nivel sobre las imágenes sensadas. Alrededor de esta matriz se localiza circuitería periférica que realiza labores de control, polarización y configuración de dicha matriz. A nivel comercial, el mejor exponente de esta estructura hardware son los sensores inteligentes diseñados por la compañía "Innovaciones Microelectrónica S.L", comercialmente conocida como Anafocus [Innovaciones Microelectrónicas S.L, www.anafocus.comí A nivel académico, numerosos grupos de investigación de diferentes países han propuesto sensores inteligentes que integran elementos fotosensibles, como por ejemplo fotodiodos, con circuitería a nivel de pixel capaz de manejar tanto señales analógicas como digitales (señal mixta) con el objeto de pre-procesar imágenes [Nilchi A, Aziz J, Genov R. *Focal- planealgorithmically-multiplying CMOS computationalimage sensor," IEEE J. Solid- StateCircuits 2009; 44(6).1829-1839];[ Jendemalik W, Blakiewicz G, Jakusz J, Szczepanski S, Piotrowski R. "Ananalog sub-miliwatt CMOS image sensor with pixel- levelconvolutionprocessing," IEEE Trans. CircuitsSyst. I 2013; 60(2):279-289];[ Femández- Bemi J, Carmona-Galan R. "AII-MOS implementation of RC networksfor time- controiiedGaussianspatialFiltering," Int. J. of CircuitTheory and Applications 2012; 40(8):859- 876];[Gottardi M, Massari N, Jawed SA. `A 100W 12864 pixelscontrast-

basedasynchronousbinaryvisión sensor for sensor networksapplications," IEEE J. Solid- StateCircuits 2009; 44(5):1582-1592];[ Leñero-Bardallo JA, Serrano-Gotarredona T, Linares- Barranco B. "A 3.6us latencyasynchronousframe-freeevent-drivendynamic-vision-sensor," IEEE J. Solid-StateCircuits 2011; 46(6):1443-1455].

Si nos centramos exclusivamente en la operación de cómputo de la imagen integral basada en la arquitectura de sensado-procesamiento que acabamos de describir, no hemos encontrado ninguna referencia proponiendo una implementación remotamente similar. Sí se pueden citar dos ejemplos de incorporación del cálculo de la imagen integral sobre un sensor inteligente [Hoseini YD, Sayedi SM, Sadri S. "A novel CMOS image sensor for high speed parallel integral image computation," 21 st Iranian Conference on Electrical Engineering (ICEE), 2013];[Jing-Shan Liang, Chien-Hong Lin, Tzu-Fang Lee, Kuo-Yu Chuang. "Image sensor having output of integral image," US patent US 2010/0238312 A1], pero en ambos casos la operación no está basada en una matriz de elementos de sensado- procesamiento donde el procesamiento se realice de forma masivamente paralela. En estos chips, los sensores conforman una matriz exclusivamente de sensado, enviándose la información que captan a la periferia de dicha matriz donde se procesa de forma agregada.

DESCRIPCIÓN DE LA INVENCIÓN

A modo de descripción de la invención, la estructura básica del hardware propuesto consiste en una distribución espacial regular bidimensional de celdas de sensado-procesamiento localmente interconectadas. Esta interconexión es reconfigurada de manera independiente para cada par de filas y columnas adyacentes mediante circuitería de control periférica.

En ella se presenta una agrupación de celdas elementales de sensado-procesamiento de señal mixta interconectadas entre sí localmente. Esta interconexión puede ser activada o desactivada para cada par de columnas y filas adyacentes por medio de señales enviadas desde la periferia de la agrupación. La celda elemental de sensado-procesamiento incluye, al menos, la circuitería elemental de procesamiento para cómputo de la imagen integral, que se debe incluir en cada celda interior de la distribución espacial regular referida. Las celdas situadas en los bordes derecho e inferior de la distribución presentarían solamente un interruptor conectando al sur o al este respectivamente. La celda de la esquina inferior derecha no presentaría ningún interruptor.

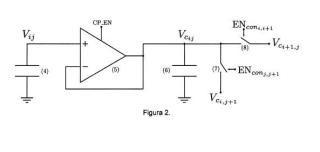

El valor de cada pixel se representa mediante el voltaje Vi¡ asociado a un condensador conectado a la entrada no inversora de un amplificador operacional cuya salida se conecta a su entrada inversora de manera que éste quede configurado como buffer analógico. Este buffer realiza la copia del voltaje ^ en la tensión VClj de un segundo condensador conectado a su salida. La operación de copia solo se realiza cuando es activada por la señal CP_EN.

Una vez completada la copia y desactivada esta señal, se activarían convenientemente las señales ENcon..+1 y ENcon^+i. La activación de estas señales, generadas de forma

independiente para cada par de columnas y filas adyacentes de la matriz por circuitería de control situada en la periferia de la agrupación, cierra sendos interruptores, provocando que 5 se produzca una redistribución de la carga almacenada en los condensadores que mantienen la copia del valor de su pixel correspondiente, esto es, VCij. Esta redistribución de

carga, por la propia naturaleza física de la operación, supone a su vez que todas las tensiones VClJ de los condensadores interconectados mediante los dos interruptores ya

citados acaben, tras dicha redistribución, manteniendo el mismo valor, que corresponderá al 10 valor promedio de los valores de pixel Vc.. previos a habilitar la interconexión. Este promedio

es directamente proporcional a la suma de dichos pixeles, y por tanto puede ser utilizado para extraer el valor de cada pixel de la imagen integral. Para el cálculo de cada uno de estos pixeles se requiere una reconfiguración de las interconexiones entre celdas acorde...

Reivindicaciones:

1.- Hardware para cómputo de la imagen integral formado por una pluralidad de celdas elementales (1) de procesamiento de señal mixta interconectadas entre sí localmente, de tal forma que cada celda está solamente interconectada con las celdas vecinas existentes al norte, sur, este y oeste, no habiendo interacción directa más allá de esa periferia; y que se caracteriza porque cada celda comprende al menos un condensador (4) cuyo voltaje representa el valor de pixel; y donde este condensador (4) se conecta al terminal no inversor de un amplificador operacional (5) cuya salida se conecta a su entrada inversora de manera que éste quede configurado como buffer analógico; y donde este amplificador operacional incorpora una señal de control que habilita la copia de la tensión de pixel fijada en el condensador (4) a su tensión de salida; y donde un condensador (6) conectado a la salida del amplificador operacional mantiene dicha copia del valor de pixel; y donde el condensador (6) se interconecta mediante interruptores (7,8) con celdas vecinas existentes al este y sur; y donde la activación/desactivación de los interruptores se realiza mediante señales digitales de control generadas en la periferia de la pluralidad de forma independiente para cada par de filas y columnas adyacentes de celdas de dicha pluralidad; y donde se produce una redistribución de la carga almacenada en el condensador (6) con los correspondientes condensadores de las celdas vecinas cuando se active cualquiera de los interruptores (7,8); y donde el valor final de tensión en el condensador (6) tras esta redistribución de carga constituye un valor directamente proporcional al de un determinado pixel de la imagen integral.

2.- Hardware para cómputo de la imagen integral según reivindicación 1, caracterizado por que el valor de la tensión del condensador (4), que representa el valor de un pixel de la imagen, puede ser copiado en cualquier momento al valor de tensión del condensador (6) mediante la activación de un señal de control del amplificador operacional (5) que los interconecta.

3.- Hardware para cómputo de la imagen integral según una cualquiera de las reivindicaciones 1 a 2, caracterizado por incorporar un condensador (6) que mantiene una copia del valor de pixel representado por la tensión en el condensador (4) y se conecta mediante interruptores (7,8) con celdas vecinas existentes al este y sur.

4.- Hardware para cómputo de la imagen integral según una cualquiera de las reivindicaciones 1 a 3, caracterizado por llevar a cabo la activación/desactivación de los interruptores (7,8) mediante señales digitales de control.

5.- Hardware para cómputo de la imagen integral según una cualquiera de las reivindicaciones 1 a 4 caracterizado por que las señales digitales de activación/desactivación de los interruptores (7,8) se generan en la periferia de la pluralidad, de manera independiente por cada par de filas y columnas adyacentes de celdas de dicha pluralidad.

6.- Método para cómputo de la imagen integral que opera sobre una pluralidad de celdas elementales (1) de procesamiento de señal mixta interconectadas entre sí localmente, de tal forma que cada celda está solamente interconectada con las celdas vecinas existentes al norte, sur, este y oeste, no habiendo interacción directa más allá de esa periferia, implementado en un hardware según se define en las reivindicaciones anteriores, caracterizado por una primera etapa de copia del valor de pixel representado por la tensión del condensador (4) en la tensión del condensador (6), haciendo uso de un amplificador operacional (5); y por una segunda etapa en la que se lleva a cabo un proceso de redistribución de la carga almacenada en el condensador (6) con la carga almacenada en otras celdas de la pluralidad determinado por señales de activación de los interruptores (7,8) provenientes de la periferia y establecidas de manera independiente por cada par de filas y columnas adyacentes de celdas de dicha pluralidad.

7.- Método para cómputo de la imagen integral según reivindicación 6, caracterizado por que la activación de los interruptores (7,8) conlleva un proceso de redistribución de la carga almacenada en la tensión del condensador (6) de cada una de las celdas de la pluralidad interconectadas por los interruptores activados.

8.- Método para cómputo de la imagen integral según una cualquiera de las reivindicaciones 6 a 7, caracterizado por que el proceso de redistribución de carga iniciado por la activación de los interruptores (7,8) conduce a un estado final de las tensiones del condensador (6) de las celdas implicadas tal que el valor de dicha tensión es el mismo para todas las celdas y coincide con el valor promedio de esas mismas tensiones antes de la activación de los interruptores.

9.- Método para cómputo de la imagen integral según una cualquiera de las reivindicaciones 6 a 8, caracterizado porque el valor promedio de tensión mantenido por el condensador (6) tras el proceso de redistribución de carga habilitado por la activación de los interruptores 5 (7,8) constituye un valor directamente proporcional al de un determinado pixel de la imagen

integral, cuya localización vendrá determinada por las filas y columnas adyacentes interconectadas mediante las señales provenientes de la periferia que controlan la activación/desactivación de los interruptores (7,8).

Patentes similares o relacionadas:

Sistema y método para clasificar materiales diferentes mediante sensor dinámico, del 27 de Mayo de 2020, de Valerio, Thomas A: Un sistema para clasificar objetos en una corriente de material de desecho movida por un sistema de transporte, el sistema que comprende:

un sensor dinámico (110; […]

Sistema y método para clasificar materiales diferentes mediante sensor dinámico, del 27 de Mayo de 2020, de Valerio, Thomas A: Un sistema para clasificar objetos en una corriente de material de desecho movida por un sistema de transporte, el sistema que comprende:

un sensor dinámico (110; […]

Detector digital, del 25 de Marzo de 2020, de Trophy: Un aparato de imágenes dentales extraorales para obtener una imagen de un paciente, comprendiendo el aparato: una fuente de radiación ; un sensor […]

Procedimiento de adquisición de imágenes por un instrumento óptico espacial o aerotransportado con un campo de visión extendido, del 2 de Octubre de 2019, de THALES: Procedimiento de adquisición de imágenes por un instrumento (IOS) óptico espacial o aerotransportado, que comprende las etapas siguientes: a) adquisición, por medio […]

Mejora de la resolución, del 4 de Septiembre de 2019, de Zhigu Holdings Limited: Sistema de detección de imágenes, que comprende: una retroiluminación ; una superficie de visualización; una válvula de luz; […]

Método y dispositivo para la detección de la variación temporal de la intensidad luminosa en una matriz de fotosensores, del 19 de Noviembre de 2018, de CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC): Un dispositivo para la detección de la variación temporal de la intensidad luminosa en una matriz de fotosensores, caracterizado por que al menos comprende: - una matriz […]

Dispositivo de formación de imágenes de radiación de recuento de fotones / pulsos, píxeles de detectores agrupados, del 13 de Junio de 2018, de OY AJAT LTD.: Una célula de píxeles de detectores agrupados para su uso en un dispositivo de formación de imágenes digitales de radiación de alta energía , dispuestos en estrecha […]

Disposición de sensores de imagen para detectar información de imagen para el procesamiento automático de datos de imagen, del 11 de Abril de 2018, de Xapt GmbH: Disposición de sensores de imagen para detectar informaciones de imagen para el procesamiento automático de datos de imagen con una pluralidad […]

Dispositivo fotosensible de múltiples profundidades de escena, sistema del mismo, método de expansión de profundidad de escena, y sistema de obtención de imágenes ópticas, del 26 de Julio de 2017, de Boly Media Communications (Shenzhen) Co., Ltd: Un dispositivo de detección de la luz de múltiples profundidades de campo, que comprende al menos dos capas de pixeles de detección de la luz capaces […]