GENERADOR DE BITS.

Sistema que comprende: un registro de desplazamiento con retroalimentación que tiene:

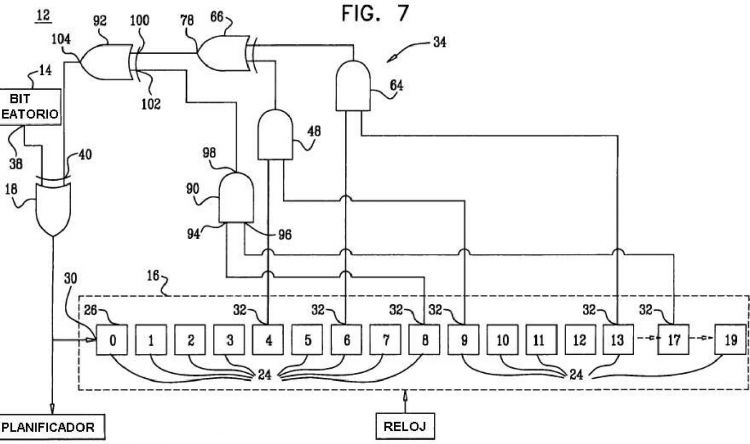

L etapas conectadas en serie que incluyen una primera etapa y una etapa final, estando denotadas las etapas de 0 a L-1, desde la primera etapa a la etapa final, respectivamente, estando operativas las etapas para almacenar una pluralidad de bits, de manera que cada una de las etapas está operativa para almacenar uno de los bits; y un reloj conectado operativamente al registro de desplazamiento con retroalimentación, estando operativo el reloj para controlar el movimiento de los bits a lo largo de las etapas; un sub-sistema de retroalimentación no lineal, teniendo al menos algunas de las etapas una salida conectada operacionalmente al sub-sistema de retroalimentación no lineal, caracterizado porque el sub-sistema de retroalimentación no lineal está operativo para recibir una entrada desde una etapa n, una etapa 2n+1, una etapa m, una etapa 2m+1, una etapa k y una etapa 2k+1 de entre las etapas, siendo n, m y k diferentes, incluyendo el sub-sistema de retroalimentación no lineal (i) una primera puerta lógica AND, teniendo la primera puerta lógica AND: una primera entrada conectada operacionalmente a la salida de la etapa n; una segunda entrada conectada operacionalmente a la salida de la etapa 2n+1; y una salida; (ii) una segunda puerta lógica AND y una primera puerta lógica XOR, teniendo la segunda puerta lógica AND: una primera entrada conectada operacionalmente a la salida de la etapa m; una segunda entrada conectada operacionalmente a la salida de la etapa 2m+1; y una salida, teniendo la primera puerta lógica XOR: una primera entrada conectada operacionalmente a la salida de la primera puerta lógica AND; y una segunda entrada conectada operacionalmente a la salida de la segunda puerta lógica AND; una tercera puerta lógica AND y una segunda puerta lógica XOR, teniendo la tercera puerta lógica AND: una primera entrada conectada operacionalmente a la salida de la etapa k; una segunda entrada conectada operacionalmente a la salida de la etapa 2k+1; y una salida, teniendo la segunda puerta lógica XOR: una primera entrada conectada operacionalmente a la salida de la primera puerta lógica XOR; una segunda entrada conectada operacionalmente a la salida de la tercera puerta lógica AND; y una salida, en el que el sub-sistema de retroalimentación no lineal tiene una salida basada, al menos en parte, en un valor de la salida de la segunda puerta lógica XOR, y teniendo además el registro de desplazamiento con retroalimentación: un generador de bits que tiene una salida, estando operativo el generador de bits para generar una pluralidad de bits aleatorios/pseudo-aleatorios para presentarlos en la salida del generador de bits; y una puerta lógica XOR principal que tiene una primera entrada y una segunda entrada y una salida, estando conectada operacionalmente la salida del generador de bits a la primera entrada de la puerta lógica XOR principal, estando conectada operacionalmente la salida del subsistema de retroalimentación no lineal a la segunda entrada de la puerta lógica XOR principal, estando conectada operacionalmente la salida de la puerta lógica XOR principal a la entrada de la primera etapa del registro de desplazamiento con retroalimentación

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/IB2008/052574.

Solicitante: NDS LIMITED.

Nacionalidad solicitante: Alemania.

Dirección: FORRESTER & BOEHMERT PETTENKOFERSTRASSE 20-22 80336 MUNICH ALEMANIA.

Inventor/es: KALUZHNY,URI.

Fecha de Publicación: .

Fecha Solicitud PCT: 26 de Junio de 2008.

Fecha Concesión Europea: 13 de Octubre de 2010.

Clasificación Internacional de Patentes:

- G06F7/58P

Clasificación PCT:

- G06F7/58 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Generadores de números aleatorios o seudoaleatorios.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia.

Fragmento de la descripción:

CAMPO DE LA INVENCIÓN

La presente invención se refiere a generadores de bits aleatorios o pseudoaleatorios, y en particular, a registros de desplazamiento con retroalimentación no lineal.

ANTECEDENTES DE LA INVENCIÓN

A modo de introducción, el uso de retrasos aleatorios, también conocidos como estados de espera aleatorios, es propuesto frecuentemente como una contramedida genérica contra análisis de canal lateral y ataques por fallos, bloqueando una CPU durante la ejecución de software incrustado. La eficiencia de un esquema de desencadenamiento de retrasos aleatorios mejora conforme incrementa la varianza de los estados de espera aleatorios. Sin embargo, los sistemas incorporan, típicamente, estados de espera aleatorios que están distribuidos uniformemente.

Se considera que las referencias siguientes representan también el estado de la técnica:

Patente US 6.167.553 concedida a Dent; Patente US 6.785.389 concedida a Sella, et al.; Solicitud de patente US publicada 2003/0085286 de Kelley, et al.; Solicitud de patente US publicada 2004/0076293 de Smeets, et al.; Solicitud de patente US publicada 2004/0205095 de Gressel, et al.; Solicitud de patente US publicada 2006/0161610 de Goettfert, et al.; Artículo titulado "Efficient Use of Random Delays" por Olivier Benoit y Michael Tunstall of Royal Holloway, Universidad de Londres; Capítulo 6 del libro Applied Cryptography (CRC Press Series on Discrete Mathematics and Its Applications) por Alfred J. Menezes, Paul C. van Oorschot y Scott A. Vanstone.

Las divulgaciones de todas las referencias indicadas anteriormente y a lo largo de la presente especificación, así como las divulgaciones de todas las referencias indicadas en esas referencias, se incorporan a la presente memoria, por referencia.

RESUMEN DE LA INVENCIÓN

La presente invención busca proporcionar un registro de desplazamiento con retroalimentación mejorado.

De esta manera, se proporciona, según una realización preferente de la presente invención, un sistema que incluye un registro de desplazamiento con retroalimentación que tiene L etapas conectadas en serie, que incluyen una primera etapa y una etapa final, estando denotadas las etapas de 0 a L-1, desde la primera etapa a la etapa final, respectivamente, estando operativas las etapas para almacenar una pluralidad de bits, de manera que cada una de las etapas es operativa para almacenar uno de los bits, y un sub-sistema de retroalimentación no lineal, teniendo al menos algunas de las etapas una salida conectada operacionalmente al sub-sistema de retroalimentación no lineal, estando operativo el sub-sistema de retroalimentación no lineal para recibir una entrada desde una etapa n y una etapa 2n-1 de entre las etapas, incluyendo el sub-sistema de retroalimentación no lineal una primera puerta lógica AND, teniendo la primera puerta lógica AND una primera entrada conectada operacionalmente a la salida de la etapa n, una segunda entrada conectada operacionalmente a la salida de la etapa 2n+1, y una salida, teniendo el sub-sistema de retroalimentación no lineal una salida basada, al menos en parte, en un valor de la salida de la primera puerta lógica AND, un reloj conectado operacionalmente al registro de desplazamiento con retroalimentación, estando operativo el reloj para controlar el movimiento de los bits a lo largo de las etapas, un generador de bits que tiene una salida, estando operativo el generador de bits para generar una pluralidad de bits aleatorios/pseudo aleatorios para ser presentados en la salida del generador de bits, y una puerta lógica XOR principal que tiene una primera entrada y una segunda entrada y una salida, estando conectada operacionalmente la salida del generador de bits a la primera entrada de la puerta lógica XOR principal, estando conectada operacionalmente la salida del sub-sistema de retroalimentación no lineal a la segunda entrada de la puerta lógica XOR principal, estando conectada operacionalmente la salida de la puerta lógica XOR principal a la entrada de la primera etapa del registro con retroalimentación no lineal.

Además, según una realización preferente de la presente invención, el sub-sistema con retroalimentación no lineal está operativo para recibir una entrada desde una etapa m y una etapa 2m+1 de entre las etapas, el sub-sistema de retroalimentación no lineal incluye una segunda puerta lógica AND y una primera puerta lógica XOR, teniendo la segunda puerta lógica AND una primera entrada conectada operacionalmente a la salida de la etapa m, una segunda entrada conectada operacionalmente a la salida de la etapa 2m+1, y una salida, la primera puerta lógica XOR del sub-sub-sistema de retroalimentación tiene una primera entrada conectada operacionalmente a la salida de la primera puerta lógica AND, y una segunda entrada conectada operacionalmente a la salida de la segunda puerta lógica AND, y la salida del sub-sistema de retroalimentación no lineal está basada, al menos en parte, en un valor de la salida de la primera puerta lógica XOR del sub-sistema de retroalimentación no lineal.

Además, según una realización preferente de la presente invención, el sub-sistema de retroalimentación no lineal está operativo para recibir una entrada desde una etapa k y una etapa 2k+1 de entre las etapas, el sub-sistema de retroalimentación no lineal incluye una tercera puerta lógica AND y una segunda puerta lógica XOR, teniendo la tercera puerta lógica AND que tiene una primera entrada conectada operacionalmente a la salida de la etapa k, una segunda entrada conectada operacionalmente a la salida de la etapa 2k+1, y una salida, la segunda puerta lógica XOR del sub-sub-sistema de retroalimentación tiene una primera entrada conectada operacionalmente a la salida de la primera puerta lógica XOR, y una segunda entrada conectada operacionalmente a la salida de la tercera puerta lógica AND, y la salida del sub-sistema de retroalimentación no lineal está basada, al menos en parte, en un valor de la salida de la segunda puerta lógica XOR del sub-sistema de retroalimentación no lineal.

Además, según una realización preferente de la presente invención, el generador de bits está operativo de manera que la salida del generador de bits está sesgada hacia un estado de las etapas del registro de desplazamiento con retroalimentación.

Además, según una realización preferente de la presente invención, el sistema incluye un planificador que tiene una entrada conectada operacionalmente a la puerta lógica XOR principal del registro de desplazamiento con retroalimentación, estando operativo el planificador para planificar una pluralidad de datos de estados de espera recibidos en la entrada del planificador.

También se proporciona, según todavía otra realización preferente de la presente invención, un sistema de estados de espera para almacenar una pluralidad de estados de espera, incluyendo un registro de desplazamiento con retroalimentación que tiene una pluralidad de etapas conectadas en serie que incluyen una primera etapa, estando operativas las etapas para almacenar una pluralidad de bits, de manera que cada una de las etapas está operativa para almacenar uno de los bits, y un sub-sistema de retroalimentación no lineal, teniendo al menos una de las etapas una salida conectada operacionalmente al sub-sistema de retroalimentación no lineal, estando operativo el sub-sistema de retroalimentación no lineal para recibir una entrada desde al menos una de las etapas, estando operativo el sub-sistema de retroalimentación no lineal de manera que una salida del sub-sistema de retroalimentación no lineal es una función no lineal de la entrada del sub-sistema de retroalimentación no lineal, estando conectada operacionalmente la salida del sub-sistema de retroalimentación no lineal a la primera etapa, un reloj conectado operacionalmente al registro de desplazamiento con retroalimentación, estando operativo el reloj para controlar el movimiento de los bits a lo largo de las etapas, y un planificador que tiene una entrada conectada operacionalmente al registro de desplazamiento con retroalimentación, estando operativo el planificador para planificar una pluralidad de datos de estados de espera recibidos en la entrada del planificador.

También se proporciona, según todavía otra realización preferente de la presente invención, un procedimiento que incluye la provisión de un registro de desplazamiento con retroalimentación que tiene L etapas conectadas en serie que incluyen una primera etapa y una etapa final, estando denotadas las...

Reivindicaciones:

1. Sistema que comprende:

un registro de desplazamiento con retroalimentación que tiene: L etapas conectadas en serie que incluyen una primera etapa y una etapa final, estando denotadas las etapas de 0 a L-1, desde la primera etapa a la etapa final, respectivamente, estando operativas las etapas para almacenar una pluralidad de bits, de manera que cada una de las etapas está operativa para almacenar uno de los bits; y un reloj conectado operativamente al registro de desplazamiento con retroalimentación, estando operativo el reloj para controlar el movimiento de los bits a lo largo de las etapas; un sub-sistema de retroalimentación no lineal, teniendo al menos algunas de las etapas una salida conectada operacionalmente al sub-sistema de retroalimentación no lineal,

caracterizado porque el sub-sistema de retroalimentación no lineal está operativo para recibir una entrada desde una etapa n, una etapa 2n+1, una etapa m, una etapa 2m+1, una etapa k y una etapa 2k+1 de entre las etapas, siendo n, m y k diferentes, incluyendo el sub-sistema de retroalimentación no lineal (i) una primera puerta lógica AND, teniendo la primera puerta lógica AND: una primera entrada conectada operacionalmente a la salida de la etapa n; una segunda entrada conectada operacionalmente a la salida de la etapa 2n+1; y una salida;

(ii) una segunda puerta lógica AND y una primera puerta lógica XOR, teniendo la segunda puerta lógica AND: una primera entrada conectada operacionalmente a la salida de la etapa m; una segunda entrada conectada operacionalmente a la salida de la etapa 2m+1; y una salida, teniendo la primera puerta lógica XOR: una primera entrada conectada operacionalmente a la salida de la primera puerta lógica AND; y una segunda entrada conectada operacionalmente a la salida de la segunda puerta lógica AND; una tercera puerta lógica AND y una segunda puerta lógica XOR, teniendo la tercera puerta lógica AND: una primera entrada conectada operacionalmente a la salida de la etapa k; una segunda entrada conectada operacionalmente a la salida de la etapa 2k+1; y una salida, teniendo la segunda puerta lógica XOR: una primera entrada conectada operacionalmente a la salida de la primera puerta lógica XOR; una segunda entrada conectada operacionalmente a la salida de la tercera puerta lógica AND; y una salida, en el que el sub-sistema de retroalimentación no lineal tiene una salida basada, al menos en parte, en un valor de la salida de la segunda puerta lógica XOR, y teniendo además el registro de desplazamiento con retroalimentación: un generador de bits que tiene una salida, estando operativo el generador de bits para generar una pluralidad de bits aleatorios/pseudo-aleatorios para presentarlos en la salida del generador de bits; y una puerta lógica XOR principal que tiene una primera entrada y una segunda entrada y una salida, estando conectada operacionalmente la salida del generador de bits a la primera entrada de la puerta lógica XOR principal, estando conectada operacionalmente la salida del subsistema de retroalimentación no lineal a la segunda entrada de la puerta lógica XOR principal, estando conectada operacionalmente la salida de la puerta lógica XOR principal a la entrada de la primera etapa del registro de desplazamiento con retroalimentación.

2. Sistema según la reivindicación 1, en el que el generador de bits está operativo de manera que la salida del generador de bits esté sesgada según un estado de las etapas del registro de desplazamiento con retroalimentación.

3. Sistema según cualquiera de las reivindicaciones 1-2, que comprende además un planificador que tiene una entrada conectada operacionalmente a la puerta lógica XOR principal o el registro de desplazamiento con retroalimentación, estando operativo el planificador para planificar una pluralidad de estados de espera según los datos recibidos en la entrada del planificador.

4. Procedimiento que comprende: proporcionar un registro de desplazamiento con retroalimentación que tiene L etapas conectadas en serie, que incluyen una primera etapa y una etapa final, estando denotadas las etapas de 0 a L-1, desde la primera etapa a la etapa final, respectivamente, estando operativas las etapas para almacenar una pluralidad de bits, de manera que cada una de las etapas está operativa para almacenar uno de los bits; y realizar lo siguiente una pluralidad de veces:

realizar una operación de puerta lógica AND con la salida de una etapa n y una etapa 2n+1 de las etapas como entrada, proporcionando un primer resultado; realizar una operación de puerta lógica AND con la salida de una etapa k y una etapa 2k+1 de las etapas como entrada, proporcionando un segundo resultado; realizar una operación de puerta lógica AND con la salida de una etapa m y una etapa 2m+1 de las etapas como entrada, proporcionando un tercer resultado, siendo n, m y k diferentes; realizar una operación de puerta lógica XOR usando el primer resultado, el segundo resultado y el tercer resultado como entrada, proporcionando un cuarto resultado; generar un bit aleatorio/pseudo-aleatorio; realizar una operación de puerta lógica XOR con el bit y el cuarto resultado como entrada, proporcionando un quinto resultado desplazar los bits a lo largo de las etapas; e insertar el quinto resultado en la primera etapa.

5. Procedimiento según la reivindicación 4, que comprende además sesgar la generación del bit aleatorio/pseudo-aleatorio según un estado de las etapas del registro de desplazamiento con retroalimentación.

6. Procedimiento según la reivindicación 4 y la reivindicación 5, que comprende además planificar una pluralidad de estados de espera según el quinto resultado.

Patentes similares o relacionadas:

Método para generar números aleatorios y generador de número aleatorio asociado, del 19 de Febrero de 2020, de Quantum Numbers Corp: Un método para generar al menos un número aleatorio, el método comprende los pasos de: generar una corriente de tunelización de cargas desde […]

Procedimiento y sistema de generación de bits cuánticos aleatorios, del 17 de Julio de 2019, de Quantum Numbers Corp: Un procedimiento para generar una muestra de bits aleatorios mediante el uso de una barrera de tunelización cuántica que comprende un aislante intercalado […]

PROCESO PARA LA GENERACIÓN FÍSICA DE NÚMEROS ALEATORIOS UTILIZANDO UN LÁSER EMISOR DE SUPERFICIE DE CAVIDAD VERTICAL, del 9 de Mayo de 2019, de FUNDACIÓ INSTITUT DE CIÈNCIES FOTÒNIQUES: Procedimiento para la generación física de números aleatorios que comprende los pasos de: - modular la ganancia de un láser emisor de superficie de cavidad vertical periódicamente […]

Generador de números aleatorios verdaderos, del 13 de Marzo de 2019, de Trentino Sviluppo S.p.A: Un generador de números aleatorios del tipo que comprende:

- una fuente de fotones;

- uno o más detectores de fotones del tipo SPAD configurados […]

Generador de números aleatorios verdaderos, del 13 de Marzo de 2019, de Trentino Sviluppo S.p.A: Un generador de números aleatorios del tipo que comprende:

- una fuente de fotones;

- uno o más detectores de fotones del tipo SPAD configurados […]

Dispositivo y método para generar una clave de identificación, del 9 de Enero de 2019, de ICTK Holdings Co., Ltd: Un aparato para generar una clave de identificación, el aparato comprende: un generador de claves configurado para generar un bit digital basado en si […]

Autenticación de suministro de a través de respuesta al desafío de temporización, del 11 de Diciembre de 2018, de HEWLETT-PACKARD DEVELOPMENT COMPANY, L.P.: Un dispositivo de suministro reemplazable que incluye una CPU y una memoria , la memoria almacenando una clave de base , […]

Procedimiento y aparato para generador de números aleatorios, del 13 de Septiembre de 2017, de QUALCOMM INCORPORATED: Un procedimiento para generar números aleatorios para su uso en un dispositivo de comunicación inalámbrica, generándose los números aleatorios en un generador […]

Procedimiento y equipo para generar números aleatorios utilizando la arquitectura de un doble oscilador y caos de tiempo continuo, del 19 de Julio de 2017, de TUBITAK: Generador de bits aleatorios que incluye una arquitectura de doble oscilador que comprende un oscilador rápido con frecuencia rápida f(fast) […]