ESTRUCTURA DE CONTACTO A TOPE DE AREA REDUCIDA.

ESTRUCTURA DE CONTACTO A TOPE DE AREA REDUCIDA (10') QUE SE PROVEE,

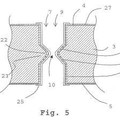

LA CUAL ES ESPECIALMENTE ADECUADA PARA CELULAS RAM ESTATICAS DE CUATRO TRANSISTORES. SE FORMA UNA ESTRUCTURA LA CUAL INCLUYE UNA REGION DOPADA DE SILICONA Y UNA O MAS CAPAS DE POLISILICONA Y OXIDO COLOCADAS ALLI ENCIMA, PUDIENDO SER UNA DE LAS CAPAS DE POLISILICONA UNA POLISILICONA DE PUERTA. ENTONCES SE REALIZA UN GRABADO POR ATAQUE QUIMICO ANISOTROPICO A TRAVES DE TODAS LAS CAPAS SUPERIORES INCLUYENDO ALGUNA CAPA SUPERIOR DE POLISILICONA LA CUAL PUEDE PRESENTARSE, PERO PARANDO EN LA REGION DOPADA DE SILICONA Y SE PRESENTA ALGUNA CAPA DE POLISILICONA DE LAS PUERTAS, PARA FORMAR UN ORIFICIO DE CONTACTO (26'). EL ORIFICIO DE CONTACTO SE LLENA CON UNA TOMA CONDUCTIVA (32) DE UN MATERIAL TAL COMO TUNGSTENO O POLISILICONA Y QUE ESTA ATACADO POR DETRAS. EN OTRO CASO, SE HACE EL CONTACTO CON TODAS LAS CAPAS DE POLISILICONA PRESENTES Y LA REGION DE SILICONA DOPADA. EN EL PROCESO DE ATAQUE ANISOTROPICO, SE EMPLEA UN ATAQUE EN DOS ETAPAS. EL PRIMER ATAQUE NO ES ESPECIFICO COMO DE UN MATERIAL, ATACANDO TODOS LOS MATERIALES (POLISILICONA Y OXIDO) EN LA MISMA TASA SUBSTANCIALMENTE Y ES CONTINUADO A TRAVES DE ALGUNA CAPA SUPERIOR DE POLISILICONA, PERO SE TERMINA ANTES DE ATACAR LA REGION DE SILICONA DOPADA O ALGUNA DE LAS CAPAS DE POLISILICONA DE LAS PUERTAS (22). EL SEGUNDO ATAQUE ES ESPECIFICO COMO DE UN MATERIAL, ATACANDO EL DIOXIDO DE SILICONA MAS RAPIDO QUE A LA POLISILICONA O A LA SILICONA, Y ASI PARA EN LA CAPA DE POLISILICONA DE LAS PUERTAS Y EN LA REGION DE SILICONA DOPADA.

Tipo: Resumen de patente/invención.

Solicitante: ADVANCED MICRO DEVICES INC..

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 901 THOMPSON PLACE P.O. BOX 3453, SUNNYVALE, CA 94088.

Inventor/es: SANDER, CRAIG S., KLEIN, RICHARD K., CHOI, TAT C.

Fecha de Publicación: .

Fecha Concesión Europea: 16 de Septiembre de 1992.

Clasificación Internacional de Patentes:

- H01L21/90

- H01L23/52 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 23/00 Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad). › Disposiciones para conducir la corriente eléctrica en el interior del dispositivo durante su funcionamiento, de un componente a otro.

Patentes similares o relacionadas:

Sistemas y métodos microelectromecánicos para encapsular y fabricar los mismos, del 4 de Diciembre de 2019, de ROBERT BOSCH GMBH: Un método para fabricar un dispositivo electromecánico que tiene estructuras (20a, 20b, 20c, 20d) mecánicas, un contacto eléctrico y regiones (22a, 22b) de campo, todas […]

Dispositivo de visualización, del 25 de Mayo de 2016, de SAMSUNG ELECTRONICS CO., LTD.: Un dispositivo de visualización que comprende un sustrato con una matriz de píxeles sobre el sustrato, electrodos de fila, electrodos de columna […]

Almacenamiento de datos y estructuras apilables, del 18 de Septiembre de 2013, de MOSAID TECHNOLOGIES INCORPORATED: Un sistema que comprende una pila incluyendo: un primer dispositivo de memoria ; un segundo dispositivo de memoria […]

Vía de interconexión de baja resistencia a través de una oblea, del 7 de Agosto de 2012, de AAC MICROTEC AB: Una oblea que comprende una vía de interconexión a través de la oblea desde una cara superior hasta una cara inferior de la […]

Vía de interconexión de baja resistencia a través de una oblea, del 7 de Agosto de 2012, de AAC MICROTEC AB: Una oblea que comprende una vía de interconexión a través de la oblea desde una cara superior hasta una cara inferior de la […]

DETERMINACION DE MASA PARA CONTROLES AUTOMATICOS DE PUERTA CORREDIZA Y LEVADIZA., del 16 de Abril de 2007, de INFINEON TECHNOLOGIES AG: Procedimiento para configurar una unidad de control de puerta de un sistema de puerta , moviéndose el sistema de puerta por medio de un dispositivo de accionamiento […]

PROCEDIMIENTO PARA LA CONEXION ELECTRICA DE MICROCHIPS DE TRANSISTOR IGBT MONTADO SOBRE UNA PLAQUETA DE CIRCUITOS INTEGRADOS., del 16 de Julio de 2006, de ALSTOM HOLDINGS: La conexión de un transistor bipolar de puerta aislada a un circuito integrado comprende la preparación y soldadura de los electrodos para unir […]

PROCEDIMIENTO DE MORDENTADO Y DISPOSITIVO PARA LA LIMPIEZA DE ELEMENTOS SEMICONDUCTORES, EN ESPECIAL DIODOS DE POTENCIA., del 1 de Enero de 1999, de ROBERT BOSCH GMBH: SE PROPONE UN PROCESO DE GRABADO DE ATAQUE ACIDO CON CHORRO DE PLASMA PARA LIMPIEZA DE UNIONES P-N EXPUESTAS LATERALMENTE EN COMPONENTES DE SEMICONDUCTOR, […]

PROCEDIMIENTO DE MANDO DEL ESTADO DE CONDUCCION DE UN TRANSISTOR MOS Y UN CIRCUITO INTEGRADO QUE PONE EN OPERACION DICHO PROCEDIMIENTO., del 1 de Abril de 1997, de BULL S.A.: EL ESTADO DE CONDUCCION DE UN TRANSISTOR MOS 11 ESTA GOBERNADO DEFINITIVAMENTE POR UN HAZ LASER 21 FORMANDO ENTRE LA REJILLA 16 Y LA PARTE SUBYACENTE […]