ENTRELAZADOR CONVOLUCIONAL CON REQUISITOS REDUCIDOS DE MEMORIA, Y GENERADOR DE DIRECCIONES PARA ESTE.

UN INTERCALADOR CONVOLUCIONAL Y ESQUEMA DE LOCALIZACION. HASTA B SIMBOLOS CONSECUTIVOS QUE CONTIENEN ERRORES PUEDEN SER INTERCALADOS DE MANERA QUE SEAN SEPARADOS ENTRE SI POR,

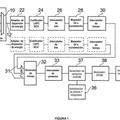

AL MENOS, N SIMBOLOS INVOLUCRADOS. UNA MEMORIA, COMO RAM, ES CONFIGURADA PARA PROPORCIONAR CELULAS (B-1) DE TAMAÑO CRECIENTE PARA ALMACENAR SIMBOLOS DE UNA FLUJO DE DATOS. UNA PRIMERA DE LAS CELULAS (CELULA 1) TIENE LOCALIZACIONES DE ALMACENAMIENTO ADAPTADAS PARA ALMACENAR M SIMBOLOS. CADA UNA DE LAS CELULAS SUCESIVAS (CELULA 2, CELULA 3) TIENE M LOCALIZACIONES DE ALMACENAMIENTO MAS QUE LA CELULA INMEDIATAMENTE PRECEDENTE PARA ALMACENAR M SIMBOLOS MAS QUE LA CELULA INMEDIATAMENTE PRECEDENTE, DONDE M = N/B. LAS CELULAS SON LOCALIZADAS SUCESIVAMENTE PARA REGISTRAR UN SIMBOLO SIGUIENTE DEL FLUJO A UNA LOCALIZACION DE SIMBOLOS DE REGISTRO SIGUIENTE EN UNA CELULA ACTUALMENTE LOCALIZADA Y PARA LEER UN SIMBOLO DE LOCALIZACION DE LA CELULA ACTUALMENTE LOCALIZADA, SIGUIENDO INMEDIATAMENTE LA LOCALIZACION DE SIMBOLO DE REGISTRO SIGUIENTE. SE ACCEDE A LAS LOCALIZACIONES EN UNA PRIMERA MANERA DE ROTACION, DE FORMA QUE LA ULTIMA LOCALIZACION EN LA CELULA ES SEGUIDA POR LA PRIMERA LOCALIZACION EN ESA CELULA. LAS CELULAS SON LOCALIZADAS EN UNA SEGUNDA FORMA ROTATORIA DE MANERA QUE LA CELULA (B-1) , ES SEGUIDA POR UNA PRIMERA CELULA O VICEVERSA. UN PASO DE TRANSFERENCIA INVOLUCRADA, PUEDE SER PROPORCIONADO DENTRO DE EL RAM ENTRE LA CELULA (B-1) LA PRIMERA CELULA PARA TRANSFERIR DIRECTAMENTE EL SIGUIENTE SIMBOLO A LA SALIDA DEL INTERCALADOR. CADA SIMBOLO CONSECUTIVO DEL FLUJO ES REGISTRADO EN UNA DE LAS CELULAS CONSECUTIVAS SIGUIENTES. SE PROPORCIONA UN DESINTERCALADOR QUE TIENE LA MISMA ESTRUCTURA.

Tipo: Resumen de patente/invención.

Solicitante: GENERAL INSTRUMENT CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 101 TOURNAMENT DRIVE, HORSHAM, PA 19044.

Inventor/es: HUANG, ZHENG.

Fecha de Publicación: .

Fecha Concesión Europea: 5 de Febrero de 2003.

Clasificación Internacional de Patentes:

- H03M13/27 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 13/00 Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C). › usando técnicas de entrelazado.

Patentes similares o relacionadas:

Método y aparato para la transmisión inalámbrica de datos sujetos a bloqueos de señal periódicos, del 6 de Mayo de 2020, de Hughes Network Systems, LLC: Un método, que comprende: segmentar (S311, S321, S331) un flujo de datos en paquetes de un tamaño fijo para una transmisión en modo ráfaga a través de […]

Método y aparato para la transmisión inalámbrica de datos sujeta a bloqueos de señal periódicos, del 23 de Octubre de 2019, de Hughes Network Systems, LLC: Un método para la transmisión inalámbrica de una primera corriente de datos, estando la transmisión sujeta a bloqueos periódicos, el método que comprende: segmentar una […]

Aparato y método de procesamiento de datos, del 25 de Septiembre de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos operable para mapear símbolos de datos recibidos de un número predeterminado de señales de subportadoras de símbolos […]

Aparato y método de procesamiento de datos, del 25 de Septiembre de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos operable para mapear símbolos de datos recibidos de un número predeterminado de señales de subportadoras de símbolos […]

Intercalador de bits para un sistema de BICM con códigos de QC-LDPC, del 3 de Julio de 2019, de PANASONIC CORPORATION: Un procedimiento de intercalación de bits para intercalar bits de una palabra de código generada en base a un esquema de codificación de comprobación de paridad de baja densidad […]

Aparato y método de procesamiento de datos, del 8 de Mayo de 2019, de Saturn Licensing LLC: Un aparato de procesamiento de datos para mapear símbolos recibidos desde un número predeterminado de señales de subportadoras de un símbolo multiplexado por división ortogonal […]

Intercalador de bits para un sistema de BICM con códigos QC LDPC, del 6 de Marzo de 2019, de PANASONIC CORPORATION: Un procedimiento de entrelazado de bits para entrelazar bits de una palabra de código generada basándose en un esquema de codificación de verificación de paridad de baja densidad […]

Entrelazador de bits para un sistema BICM con códigos QC LDPC, del 28 de Febrero de 2019, de PANASONIC CORPORATION: Un método de entrelazado de bits para entrelazar bits de una palabra de código generada en base a un esquema de codificación con comprobación de paridad de baja densidad […]

Método de codificación del código polar y dispositivo de codificación, del 27 de Febrero de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de codificación del código polar, caracterizado por comprender: asignar M bits reservados de una señalización de difusión a M bits […]