CIRCUITO DE CONTROL PARALELO Y DISPOSITIVO SEMICONDUCTOR.

Un circuito monitor en paralelo (1A) para monitorizar uno de una pluralidad de capacitores conectados en serie (C1,

C2) que reciben una corriente de recarga directa, que comprende un transistor de derivación (Q1) para sortear el capacitor (C1) con la corriente de recarga cuando la tensión de un capacitor supera una tensión de monitor determinada por un circuito de control de tensión con el fin de recargar igualmente los capacitores, una unidad de transferencia (Decodificador 13) para transferir un circuito de ajuste de tensión (VS1) y un circuito interno (CMP11, CMP12) conectado al circuito de ajuste de tensión (VS1) a un modo en espera cuando el circuito de ajuste de tensión (VS1) recibe una combinación específica de códigos de tensión (RC1a a RC1d), y caracterizado porque se detecta una tensión de capacitor negativa y se detecta un funcionamiento anómalo mediante el circuito interno (CMP12) después de que el circuito interno ha sido transferido al modo en espera y se ha interrumpido la detección de tensión

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E05251960.

Solicitante: RICOH COMPANY, LTD..

Nacionalidad solicitante: Japón.

Dirección: 3-6, NAKAMAGOME 1-CHOME, OHTA-KU,TOKYO 143-8555.

Inventor/es: YANO,KOICHI, FUJIWARA,AKIHIKO.

Fecha de Publicación: .

Fecha Solicitud PCT: 30 de Marzo de 2005.

Fecha Concesión Europea: 2 de Junio de 2010.

Clasificación Internacional de Patentes:

- H02J13/00E

- H02J7/00C1B

- H02J7/34C

- H02J9/00S

Clasificación PCT:

- H02J7/06 ELECTRICIDAD. › H02 PRODUCCION, CONVERSION O DISTRIBUCION DE LA ENERGIA ELECTRICA. › H02J CIRCUITOS O SISTEMAS PARA LA ALIMENTACION O LA DISTRIBUCION DE ENERGIA ELECTRICA; SISTEMAS PARA EL ALMACENAMIENTO DE ENERGIA ELECTRICA. › H02J 7/00 Circuitos para la carga o despolarización de baterías o para suministrar cargas desde baterías. › utilizando tubos de descarga o dispositivos semiconductores.

Clasificación antigua:

- H02J7/06 H02J 7/00 […] › utilizando tubos de descarga o dispositivos semiconductores.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

Circuito de control paralelo y dispositivo semiconductor.

Antecedentes de la invención

La presente invención se refiere en general a un circuito monitor en paralelo y un aparato de semiconductores que tiene dicho circuito monitor en paralelo para monitorizar uno de varios capacitores eléctricos de doble capa conectados en serie con el fin de recargar igualmente los capacitores, y específicamente se refiere a dicho circuito monitor en paralelo en el que puede variarse una tensión de monitor para cambiar el circuito a un modo en espera.

Un capacitor eléctrico de doble capa puede recargarse rápidamente, en comparación con una batería secundaria que requiere una gran cantidad de tiempo para la recarga. Además, el capacitor eléctrico doble tiene una ventaja que no alcanza la batería secundaria, ya que puede almacenar una gran cantidad de energía. Sin embargo, el capacitor eléctrico de doble capa tiene una tensión nominal baja de 2,7 V, y por tanto habitualmente se conectan en serie varios capacitores para conseguir la alta tensión necesaria.

Así, los varios capacitores conectados en serie tienen el problema de que la recarga no es uniforme o igual para cada capacitor debido a la variación de capacitancia, auto-recarga, auto-descarga, etc.

Con el fin de abordar el problema de la recarga desigual, normalmente se usa un circuito igualador de recarga denominado "circuito monitor en paralelo".

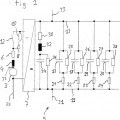

La Fig. 4 es un diagrama de circuitos de una parte de dicho circuito monitor en paralelo desvelado en la patente japonesa nº 3.313.647.

Aunque la Fig. 4 sólo muestra un circuito monitor en paralelo, habitualmente se emplea una pluralidad de circuitos monitores en paralelo conectados en serie. Cada uno de los circuitos monitores en paralelo se conecta a un capacitor. Los circuitos monitores en paralelo tienen la misma estructura, por tanto, a continuación se da una explicación con respecto sólo a un circuito monitor en paralelo.

Como se muestra en la Fig. 4, el circuito monitor en paralelo comprende dos suministros de tensión de referencia Vr1 y Vr2, un circuito comparador CMP para comparar estas tensiones de referencia con la tensión de un capacitor C1, dos conmutadores S1 y S2 para conmutar la conexión a las tensiones de referencia Vr1 y Vr2, un transistor Tr1 para sortear el capacitor C1 con una corriente eléctrica para recargar el capacitor C1, y un circuito de control de conmutación.

La tensión de referencia Vr1 se ajusta a 3 V que es la misma que la tensión de plena recarga para el capacitor C1. La tensión de referencia Vr2 se ajusta a 0,8 V, menor que la tensión de plena recarga. En la fase inicial del procedimiento de recarga, el conmutador S1 se conecta a la tensión de referencia Vr2 (0,8 V). Cuando la tensión del capacitor C1 alcanza 0,8 V, la salida del circuito comparador CMP se invierte a H, activando el transistor Tr1. Después de que se activa el transistor Tr1, el capacitor C1 se descarga con una constante de tiempo que está determinada por factores de resistencia que incluyen el transistor Tr1.

El circuito de control de conmutación monitoriza las salidas de todos los circuitos comparadores CMP. Mientras el capacitor C1 se está descargando, si cualquier otro capacitor Cn alcanza 0,8 V, los conmutadores del circuito de control de conmutación conmutan S1 a la tensión de referencia Vr1 para liberar el modo de derivación para el capacitor C1 y recargar el capacitor C1 hasta la tensión de plena recarga de 3 V.

En dichos circuitos monitores en paralelo convencionales, la energía eléctrica es suministrada siempre al circuito comparador CMP incluso aunque no se realice el control de recarga, con el resultado de un derroche de consumo de energía, lo que supone un problema.

En general, se conoce un modo en espera para ahorrar energía para resolver el problema anterior. En dicho modo en espera, aunque los circuitos incluidos en un aparato de semiconductores no se requieren para funcionar, el funcionamiento del circuito se detiene y la energía suministrada se reduce. Sin embargo, con el fin de cambiar o transferir el aparato de semiconductores al modo en espera, es necesario que el aparato de semiconductores tenga un terminal en espera, a través del cual un circuito de control externo que incluye una CPU suministra una señal de espera al aparato de semiconductores.

Sin embargo, dado que los circuitos monitores en paralelo reciben señales de control del circuito de control externo para controlar la recarga de muchos capacitores conectados a los mismos, necesitan muchos terminales. El número de terminales es muy importante cuando un aparato de semiconductores que incluye dichos circuitos monitores en paralelo se encapsula en un paquete de uso genérico.

En más detalle, para controlar paso por paso desde el CI más bajo al CI más alto entre el aparato de semiconductores conectado en serie, se necesitan dos terminales para una señal. Cuando es necesaria una pluralidad de controles de estado, dos terminales para activación/desactivación de un estado conllevan altos costes de fabricación, complejos diseños de circuitos y una gran zona para la tarjeta de conexiones.

Si el número de terminales necesarios es superior al número de terminales de un paquete de uso genérico en sólo uno, debe usarse un paquete más grande y más caro.

El documento WO-02/097.945 desvela un sistema para gestión de energía en una serie de unidades de almacenamiento de energía en las que se monitoriza la corriente suministrada a las unidades de almacenamiento de energía y la corriente se desvía de una unidad de almacenamiento de energía a otra en respuesta a la velocidad de carga y a la capacidad de la unidad de almacenamiento de energía.

Resumen de la invención

En consecuencia, un objeto general de la presente invención es proporcionar un circuito monitor en paralelo y un aparato de semiconductores que emplea el circuito monitor en paralelo, en el que la monitorización puede producirse durante un modo en espera, de acuerdo con las reivindicaciones 1 y 5 respectivamente.

En la descripción mostrada a continuación se exponen las características y ventajas de la presente invención, y en parte serán evidentes a partir de la descripción y de los dibujos adjuntos, o pueden aprenderse mediante la práctica de la invención según las enseñanzas proporcionadas en la descripción. Los objetos, así como las características y ventajas de la presente invención, se realizarán y alcanzarán mediante un circuito monitor en paralelo expuesto en particular en la memoria descriptiva en términos tan completos, claros, concisos y exactos que permiten que el experto en la materia pueda poner en práctica la invención.

Para conseguir estas y otras ventajas y de acuerdo con el fin de la invención, según se expone y describe ampliamente en este documento la invención se proporciona del modo siguiente.

Según un primer aspecto de la presente invención se proporciona un circuito monitor en paralelo para monitorizar uno de una pluralidad de varios capacitores conectados en serie que reciben una corriente de recarga directa, que comprenden un transistor de derivación para sortear el capacitor con la corriente de recarga cuando la tensión de un capacitor supera una tensión de monitor determinada por un circuito de control de tensión con el fin de recargar igualmente los capacitores, una unidad de transferencia para transferir un circuito de ajuste de tensión y un circuito interno conectado al circuito de control de tensión en un modo en espera cuando el circuito de ajuste de tensión recibe una combinación específica de códigos de tensión, y caracterizado porque se detecta una tensión de capacitor negativa y se detecta funcionamiento anómalo mediante el circuito interno después de que el circuito interno se ha transferido al modo en espera y se ha interrumpido la detección de tensión.

Preferentemente se emite una señal de espera cuando todos los bits de los códigos de tensión tienen valor alto.

Preferentemente, la entrada de los códigos de tensión al circuito de ajuste de tensión puede usarse para proporcionar señales de control de estado que no requieren código de ajuste de tensión, usando terminales de control para conectar varios aparatos de semiconductores, sin añadir un terminal dedicado.

Preferentemente, se usan líneas de señales y terminales de control para conectar una pluralidad...

Reivindicaciones:

1. Un circuito monitor en paralelo (1A) para monitorizar uno de una pluralidad de capacitores conectados en serie (C1, C2) que reciben una corriente de recarga directa, que comprende un transistor de derivación (Q1) para sortear el capacitor (C1) con la corriente de recarga cuando la tensión de un capacitor supera una tensión de monitor determinada por un circuito de control de tensión con el fin de recargar igualmente los capacitores, una unidad de transferencia (Decodificador 13) para transferir un circuito de ajuste de tensión (VS1) y un circuito interno (CMP11, CMP12) conectado al circuito de ajuste de tensión (VS1) a un modo en espera cuando el circuito de ajuste de tensión (VS1) recibe una combinación específica de códigos de tensión (RC1a a RC1d), y caracterizado porque se detecta una tensión de capacitor negativa y se detecta un funcionamiento anómalo mediante el circuito interno (CMP12) después de que el circuito interno ha sido transferido al modo en espera y se ha interrumpido la detección de tensión.

2. El circuito monitor en paralelo (1A) según la reivindicación 1, caracterizado porque se proporciona un medio por el que se produce una señal de espera cuando todos los bits de los códigos de tensión (RC1a a RC1d) tienen valor alto.

3. El circuito monitor en paralelo (1A) según la reivindicación 1, caracterizado porque los códigos de tensión (RC1a a RC1d) de entrada al circuito de ajuste de tensión (VS1) pueden usarse para proporcionar señales de control de estado que no requieren código de ajuste de tensión, usando terminales de control (ASG, ASGB) para conectar varios aparatos de semiconductores, sin añadir un terminal dedicado.

4. El circuito monitor en paralelo (1A) según la reivindicación 1, caracterizado porque se usan líneas de señales (RCa-RCd) y terminales de control (ASG, ASGB) para conectar una pluralidad de aparatos de semiconductores, sin añadir un terminal dedicado.

5. Un aparato de semiconductores que tiene una pluralidad de los circuitos monitores en paralelo (1A) según la reivindicación 1.

Patentes similares o relacionadas:

PROCEDIMIENTO DE CARGA EQUILIBRADA DE UNA BATERIA DE ION LITIO O POLIMERO DE LITIO, del 17 de Junio de 2010, de PELLENC (SOCIETE ANONYME): Procedimiento de cargado equilibrado de n celdas, con n =q 2 constitutivos de una batería ión-litio o polímero de litio y asociadas en serie, estando compuesta […]

PROCEDIMIENTO DE CARGA EQUILIBRADA DE UNA BATERIA DE ION LITIO O POLIMERO DE LITIO, del 17 de Junio de 2010, de PELLENC (SOCIETE ANONYME): Procedimiento de cargado equilibrado de n celdas, con n =q 2 constitutivos de una batería ión-litio o polímero de litio y asociadas en serie, estando compuesta […]

![]() DISPOSITIVO DE SEMICONDUCTOR CASCADABLE PARA LA SUPERVISION DE LA CARGA DE UN CONDENSADOR, del 17 de Marzo de 2010, de RICOH COMPANY, LTD.: Un aparato semiconductor (CI1; CI2) para controlar transistores de derivación (TR11-15; TR21-25) para cargar uniformemente una pluralidad de condensadores (C11-15; […]

DISPOSITIVO DE SEMICONDUCTOR CASCADABLE PARA LA SUPERVISION DE LA CARGA DE UN CONDENSADOR, del 17 de Marzo de 2010, de RICOH COMPANY, LTD.: Un aparato semiconductor (CI1; CI2) para controlar transistores de derivación (TR11-15; TR21-25) para cargar uniformemente una pluralidad de condensadores (C11-15; […]

METODO Y APARATO PARA CONTROLAR LA TRANSFERENCIA DE ENERGIA ENTRE UNA BARRA COLECTORA DE ENERGIA Y UN SISTEMA DE BATERIAS A BASE DE UNA CON DICION DE OPERACION DE BATERIA, del 26 de Noviembre de 2009, de AZURE DYNAMICS INC.: Método para controlar la transferencia de energía entre una barra colectora de energía y un sistema de baterías que consiste en una cadena en […]

METODO Y APARATO PARA CONTROLAR LA TRANSFERENCIA DE ENERGIA ENTRE UNA BARRA COLECTORA DE ENERGIA Y UN SISTEMA DE BATERIAS A BASE DE UNA CON DICION DE OPERACION DE BATERIA, del 26 de Noviembre de 2009, de AZURE DYNAMICS INC.: Método para controlar la transferencia de energía entre una barra colectora de energía y un sistema de baterías que consiste en una cadena en […]

DISPOSITIVO PERFECCIONADO APLICABLE A LUCES DE EMERGENCIA, del 10 de Febrero de 2011, de VENTAYOL Y PINYOL, JOAN: Dispositivo perfeccionado aplicable a luces de emergencia.El dispositivo perfeccionado para luces de emergencia estará formado por unos […]

DISPOSITIVO PERFECCIONADO APLICABLE A LUCES DE EMERGENCIA, del 10 de Febrero de 2011, de VENTAYOL Y PINYOL, JOAN: Dispositivo perfeccionado aplicable a luces de emergencia.El dispositivo perfeccionado para luces de emergencia estará formado por unos […]

ALIMENTACION ININTERRUMPIDA Y PROCEDIMIENTO DE PUESTA EN PRACTICA DE DICHA ALIMENTACION, del 14 de Mayo de 2010, de MGE-UPS SYSTEMS: Alimentación ininterrumpida que comprende:

- por lo menos una primera entrada destinada a ser conectada a una primera fuente de una tensión alterna (VACin1),

- […]

ALIMENTACION ININTERRUMPIDA Y PROCEDIMIENTO DE PUESTA EN PRACTICA DE DICHA ALIMENTACION, del 14 de Mayo de 2010, de MGE-UPS SYSTEMS: Alimentación ininterrumpida que comprende:

- por lo menos una primera entrada destinada a ser conectada a una primera fuente de una tensión alterna (VACin1),

- […]

SISTEMA PARA EL AHORRO DE ENERGIA, del 29 de Enero de 2010, de ASTRAL POOL GROUP, S.L.U.: Sistema para el ahorro de energía. Se caracteriza porque comprende un convertidor digital de energía renovable como fuente de alimentación, y un modulador estándar […]

SISTEMA PARA EL AHORRO DE ENERGIA, del 29 de Enero de 2010, de ASTRAL POOL GROUP, S.L.U.: Sistema para el ahorro de energía. Se caracteriza porque comprende un convertidor digital de energía renovable como fuente de alimentación, y un modulador estándar […]

MÉTODO Y APARATO PARA LA TRANSFERENCIA DE POTENCIA ELÉCTRICA, del 21 de Junio de 2011, de BOMBARDIER TRANSPORTATION GMBH: Dispositivo para la transferencia de potencia eléctrica desde una fuente de potencia a un punto de consumo eléctrico , en particular, a un motor de impulsión […]

MÉTODO Y APARATO PARA LA TRANSFERENCIA DE POTENCIA ELÉCTRICA, del 21 de Junio de 2011, de BOMBARDIER TRANSPORTATION GMBH: Dispositivo para la transferencia de potencia eléctrica desde una fuente de potencia a un punto de consumo eléctrico , en particular, a un motor de impulsión […]

SISTEMA DE ALMACENAMIENTO DE ENERGIA PARA ALIMENTAR DISPOSITIVOS ELECTRICOS DE USUARIO DE UN VEHICULO, del 5 de Abril de 2010, de MAGNETI MARELLI POWERTRAIN S.P.A.

ENEA-ENTE PER LE NUOVE TECNOLOGIE, L'ENERGIA E L'AMBIENTE: Sistema de almacenamiento de energía para alimentar dispositivos eléctricos de usuario de un vehículo híbrido; comprendiendo el sistema de almacenamiento […]

SISTEMA DE ALMACENAMIENTO DE ENERGIA PARA ALIMENTAR DISPOSITIVOS ELECTRICOS DE USUARIO DE UN VEHICULO, del 5 de Abril de 2010, de MAGNETI MARELLI POWERTRAIN S.P.A.

ENEA-ENTE PER LE NUOVE TECNOLOGIE, L'ENERGIA E L'AMBIENTE: Sistema de almacenamiento de energía para alimentar dispositivos eléctricos de usuario de un vehículo híbrido; comprendiendo el sistema de almacenamiento […]