ARQUITECTURA DE MEMORIA FLASH QUE IMPLEMENTA MULTIPLES BANCOS DE MEMORIA FLASH PROGRAMABLES SIMULTANEAMENTE, QUE SON COMPATIBLES CON UNA CENTRAL.

Un sistema de memoria flash (1001) que comprende una pluralidad de bancos de memoria separados y direccionables independientemente (1020,

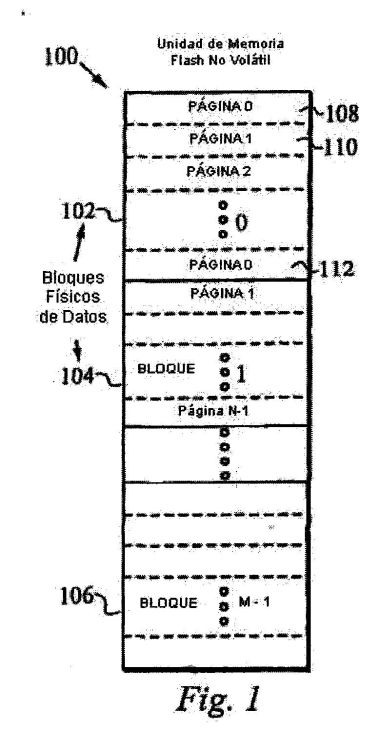

1022, 1024, 1026), cada banco de memoria (1020, 1022, 1024, 1026) comprendiendo: a. una pluralidad de áreas de almacenamiento de datos no volátiles, direccionables independientemente y programables independientemente; b. un registro de datos RAM principal (1030, 1032, 1034, 1036); y c. un valor exclusivo del fabricante, incluyendo medios para cargar el valor exclusivo del fabricante en un paquete de datos de establecimiento de conexión (1100), tras la puesta en servicio, donde el sistema de memoria flash (1001) está configurado para funcionar selectivamente en un primer nuevo de almacenamiento de datos y en un segundo modo de almacenamiento de datos, en respuesta al valor exclusivo del fabricante, el primer modo de almacenamiento de datos siendo un modo por defecto, en el que un solo ciclo de programación acorde con el primer modo de almacenamiento de datos, comprende un almacenamiento de datos en un solo registro de datos RAM, para una programación en una sola página.

Tipo: Resumen de patente/invención.

Solicitante: LEXAR MEDIA, INC.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 47421 BAYSIDE PARKWAY,FREMONT, CA 94538.

Inventor/es: ESTAKHRI,PETRO.

Fecha de Publicación: .

Fecha Solicitud PCT: 17 de Mayo de 2001.

Fecha Concesión Europea: 19 de Septiembre de 2007.

Clasificación PCT:

- G06F12/00 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06).

- G06F12/02 G06F […] › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › Direccionamiento o asignación; Traslado (secuenciación de direcciones de programa G06F 9/00; disposiciones para seleccionar una dirección en una memoria digital G11C 8/00).

- G06F12/06 G06F 12/00 […] › Direccionamiento de un bloque físico de posiciones, p. ej. por dirección de base, direccionamiento de módulos, extensión del espacio de direcciones, dedicación de memoria (G06F 12/08 tiene prioridad).

- G06K19/07 G06 […] › G06K RECONOCIMIENTO DE DATOS; PRESENTACION DE DATOS; SOPORTES DE REGISTROS; MANIPULACION DE SOPORTES DE REGISTROS (impresión per se B41J). › G06K 19/00 Soportes de registro para utilización con máquinas y con al menos una parte prevista para soportar marcas digitales. › con chips de circuito integrado.

- G11C16/02 G […] › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 16/00 Memorias de sólo lectura programables y borrables (G11C 14/00 tiene prioridad). › programables eléctricamente.

- G11C16/20 G11C 16/00 […] › Inicialización; Preselección de datos; Identificación de "chip".

- G11C16/32 G11C 16/00 […] › Circuitos de sincronización.

- G11C8/12 G11C […] › G11C 8/00 Disposiciones para seleccionar una dirección en una memoria digital (circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Circuitos de selección de grupo, p. ej. para la selección de un bloque de memoria, la selección de un circuito integrado, la selección de una red de celdas.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Patentes similares o relacionadas:

Método y aparato para un acceso a memoria basado en hilos en un procesador multihilo, del 11 de Septiembre de 2019, de QUALCOMM INCORPORATED: Método para acceder a una memoria por un procesador multihilo , comprendiendo el método: determinar un identificador de hilo asociado a un […]

Aparato de acceso a datos que usa un dispositivo de memoria, del 31 de Julio de 2019, de LSIS Co., Ltd: Un aparato de acceso a datos que utiliza un dispositivo de memoria para mapear direcciones, que comprende: un dispositivo de memoria de 8 bits que tiene una […]

Uso de compresión de memoria para reducir la carga de compromiso de memoria, del 6 de Mayo de 2019, de Microsoft Technology Licensing, LLC: Un método de reducir una cantidad de compromiso de memoria para un programa en un dispositivo de cálculo , comprendiendo el método: determinar […]

Dispositivo de memoria híbrida con una única interfaz, del 23 de Enero de 2019, de Microsoft Technology Licensing, LLC: Un procedimiento que comprende: recibir, en un controlador , órdenes, direcciones y datos en un dispositivo de memoria mediante una interfaz definida asociada […]

Controlador de acceso a memoria, sistemas y procedimientos para optimizar los tiempos de acceso a memoria, del 9 de Enero de 2019, de QUALCOMM INCORPORATED: Un controlador de memoria , que comprende: un controlador configurado para acceder al menos a una ubicación de memoria correspondiente […]

Método y aparato de extensión de particiones, del 20 de Diciembre de 2017, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de extensión de particiones, que comprende: adquirir un valor medio de cantidades de particiones en todos los nodos […]

Procedimiento y dispositivo de instalación de una aplicación MIFARE en una memoria MIFARE, del 20 de Diciembre de 2017, de IDEMIA France: Procedimiento de instalación de la aplicación MIFARE en una memoria MIFARE , estando la aplicación MIFARE de acuerdo con la norma ISO 14443A y memorizada en un […]

Procesador digital de señales y método para direccionar una memoria en un procesador digital de señales, del 18 de Octubre de 2017, de MediaTek Sweden AB: Un procesador digital de señales que comprende al menos una unidad funcional, que puede ser una unidad de ejecución de vectores , o un acelerador, […]