APARATO Y METODO MEJORADOS PARA LA MULTIPLICACION Y EXPONENCIACION MODULARES BASADAS EN LA MULTIPLICACION DE MONTGOMERY.

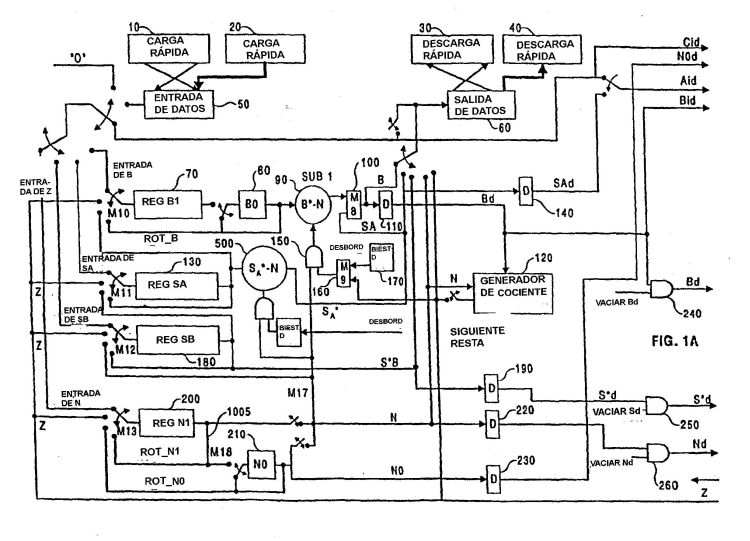

Unidad aritmético lógica (ALU) microelectrónica para realizar una multiplicación modular de tipo Montgomery de P(A·B)N,

donde P(P·B)N es modularmente congruente con A·B·I mod N, donde I es un 2-n mod N, A, B y N son operandos de n bits de longitud, siendo N impar, comprendiendo el aparato: registros de memoria principales primeros (70, 80; 1000) y segundos (200, 210; 1005), cada registro para mantener un operando de n bits de longitud, estando adaptados respectivamente dichos registros para almacenar el multiplicador, B, y el módulo N; un dispositivo (390, ...) para multiplicar de forma simultánea una primera cadena (A i) de k bits por un primer bit (B d) entrante y una segunda cadena (N 0, Y 0) de k bits por un segundo bit (Y 0, N d) entrante y acumular el resultado, teniendo el dispositivo sólo un sumador (410) con acarreo acumulado, teniendo al menos k+1 bits de longitud, estando adaptado el dispositivo para seleccionar como un valor de entrada al sumador con acarreo acumulado un valor de cadena de todo ceros, la primera cadena de k bits, la segunda cadena de k bits o la suma precalculada de la primera y segunda cadenas de k bits, estando adaptado el aparato para introducir en una primera fase: los bits menos significativos de B como primeros bits entrantes; los bits consecutivos de un valor previsto generado "sobre la marcha", Y 0, como segundos bits entrantes en el dispositivo; los k bits consecutivos del multiplicando (A) como la primera cadena de k bits; y los k bits menos significativos consecutivos de N como segunda cadena de k bits, estando adaptado el aparato para introducir en una segunda fase: los bits menos significativos consecutivos de B como primeros bits entrantes; los bits consecutivos de N, como segundos bits entrantes en el dispositivo; los k bits consecutivos del multiplicando (A) como la primera cadena de k bits; y los k bits menos significativos consecutivos de Y0, generados en la primera fase, como la segunda cadena de k bits; un dispositivo (430) lógico para determinar Y0, de manera que los k bits menos significativos enviados desde el sumador (410) con acarreo acumulado en la primera fase son ceros, recibiendo el dispositivo lógico como entradas: el bit menos significativo de la primera cadena (Ai) de k bits; el primer bit (Bd) entrante; un bit de salida de acarreo menos significativo desde el sumador (410) con acarreo acumulado; el siguiente al bit menos significativo desde el sumador (410) con acarreo acumulado; el siguiente bit desde un registro (S) de almacenamiento temporal; y un bit de salida de acarreo desde un sumador (460), estando adaptado el sumador (410) con acarreo acumulado para enviar valores de forma simultánea mientras que se suman multiplicandos en el sumador (410) con acarreo acumulado; y un mecanismo de transferencia de salida, adaptado en una segunda fase para enviar un resultado P(A-B)N final desde el sumador (410) con acarreo acumulado.

Tipo: Resumen de patente/invención.

Solicitante: FORTRESS U & T LTD.

Nacionalidad solicitante: Israel.

Dirección: YEHOSHUA HATSOREF STREET 34,84001 BEER SHEVA.

Inventor/es: HADAD,ISAAC, ARAZI,BENJAMIN, GRESSEL,CARMI,DAVID, DROR,ITAI.

Fecha de Publicación: .

Fecha Concesión Europea: 5 de Septiembre de 2007.

Clasificación PCT:

- G06F1/02 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 1/00 Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76). › Generadores de funciones digitales.

- G06F7/52 G06F […] › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Multiplicación; División (G06F 7/483 - G06F 7/491, G06F 7/544 - G06F 7/556 tienen prioridad).

- G06F7/544 G06F 7/00 […] › para la evaluación de funciones por cálculo.

- G06F7/72 G06F 7/00 […] › que utilizan la aritmética de restos.

- G09C1/00 G […] › G09 ENSEÑANZA; CRIPTOGRAFIA; PRESENTACION; PUBLICIDAD; PRECINTOS. › G09C APARATOS DE CIFRAR O DESCIFRAR PARA LA CRIPTOGRAFIA U OTROS FINES QUE IMPLICAN LA NECESIDAD DEL SECRETO. › Aparatos o métodos por medio de los cuales una sucesión dada de signos, p. ej. un texto inteligible, se transforma en una sucesión de signos ininteligibles transponiendo los signos o grupos de signos o remplazándolos por otros según un sistema preestablecido (máquinas de escribir criptográficas G09C 3/00).

Patentes similares o relacionadas:

Procedimiento de protección de circuitos electrónicos contra interceptación por análisis de potencia y circuito electrónico que usa el mismo, del 3 de Junio de 2020, de Winbond Electronics Corp: Un circuito electrónico con protección contra interceptación por análisis de potencia, que comprende: un elemento de almacenamiento […]

Procedimiento y dispositivos de protección de la introducción de un código alfanumérico, de la producción de un programa de ordenador y medios de almacenamiento correspondiente, del 20 de Mayo de 2020, de Ingenico Group: Procedimiento de protección para la introducción de un código alfanumérico por parte de un usuario durante una transacción, caracterizado por que utiliza las siguientes […]

Marca de seguridad compuesta basada en puf para antifalsificación, del 11 de Marzo de 2020, de MERCK PATENT GMBH: Una marca de seguridad compuesta para un objeto fisico, en particular una marca de producto antifalsificacion, que comprende: una funcion fisica no clonable, PUF; […]

Dispositivo de transmisión de datos y método de transmisión de datos, del 4 de Marzo de 2020, de NEC CORPORATION: Un dispositivo de transmisión de datos , que comprende: un receptor , configurado para recibir datos encriptados; un transmisor , configurado para transmitir […]

Algoritmo criptográfico con etapa de cálculo enmascarada dependiente de clave (llamada de SBOX), del 12 de Febrero de 2020, de Giesecke+Devrient Mobile Security GmbH: Unidad de procesador con una implementación ejecutable implementada en la misma de un algoritmo criptográfico (AES, DES), que está configurado para, […]

Dispositivo de lectura para leer una marca compuesta que comprende una función física no clonable para la lucha contra la falsificación, del 13 de Noviembre de 2019, de MERCK PATENT GMBH: Un metodo para leer con un dispositivo lector una marca de seguridad compuesta que comprende una funcion fisica no clonable, PUF, y una primera firma digital correspondiente […]

Un protocolo de red agile para comunicaciones seguras con disponibilidad asegurada de sistema, del 11 de Septiembre de 2019, de VirnetX Inc: Un método para un primer nodo para establecer una sesión con un segundo nodo , el método se realiza en el primer nodo , en el que […]

Instrucciones de escalado de vectores para su uso en una unidad aritmética lógica, del 24 de Julio de 2019, de QUALCOMM INCORPORATED: Un procedimiento para escalar un vector, comprendiendo el procedimiento: recibir, por al menos un procesador, componentes de un vector, en el que cada uno de los […]