Aparato y procedimiento de control de la modificación dinámica de una trayectoria de exploración.

Un aparato de sistema en chip (110, 500, 600, 800), que comprende:

una trayectoria de exploración de prueba (521, 621, 821) que comprende una pluralidad de componentes de prueba (522) que incluyen al menos un componente de prueba de habilitación de jerarquía (523, 623, 825); y

una trayectoria de exploración de control (526, 626, 823) que comprende al menos un componente de control (627, 825), estando acoplado el al menos un componente de control a dicho al menos un componente de prueba de habilitación de jerarquía de la trayectoria de exploración de prueba;

en el que el al menos un componente de control está adaptado para controlar el al menos un componente de prueba de habilitación de jerarquía de una manera para modificar dinámicamente la trayectoria de exploración de prueba,

caracterizado porque la trayectoria de exploración de control es independiente de la trayectoria de exploración de prueba.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2009/000453.

Solicitante: ALCATEL LUCENT.

Nacionalidad solicitante: Francia.

Dirección: 148/152 route de la Reine 92100 Boulogne-Billancourt FRANCIA.

Inventor/es: CHAKRABORTY,Tapan,Jyoti, CHIANG,Chen-Huan, GOYAL,Suresh, PORTOLAN,Michele, VAN TREUREN,Bradford,Gene.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G01R31/3185 FISICA. › G01 METROLOGIA; ENSAYOS. › G01R MEDIDA DE VARIABLES ELECTRICAS; MEDIDA DE VARIABLES MAGNETICAS (indicación de la sintonización de circuitos resonantes H03J 3/12). › G01R 31/00 Dispositivos para ensayo de propiedades eléctricas; Dispositivos para la localización de fallos eléctricos; Disposiciones para el ensayo eléctrico caracterizadas por lo que se está ensayando, no previstos en otro lugar (ensayo o medida de dispositivos semiconductores o de estado sólido, durante la fabricación H01L 21/66; ensayo de los sistemas de transmisión por líneas H04B 3/46). › Reconfiguración para los ensayos, p. ej. LSSD, divisiones.

PDF original: ES-2503543_T3.pdf

Fragmento de la descripción:

Aparato y procedimiento de control de la modificación dinámica de una trayectoria de exploración Campo de la invención La invención se refiere al campo de la electrónica y, más específicamente, a pruebas de placas de circuito impreso, sistemas en chips, y sistemas.

Antecedentes de la invención El Grupo de Acción de Prueba Conjunta (JTAG) se refiere a la norma IEEE 1149 para probar puertos de acceso para probar placas de circuito impreso con exploración de límites. El JTAG es utilizado mediante herramientas de Generación de Pruebas Automáticas (ATG) para probar placas de circuito impreso. El instrumento JTAG (IJTAG) está siendo estandarizado (referido como el estándar IEEE P1687) para superar las limitaciones del JTAG existentes asociadas con el paso del JTAG a nivel de placa al JTAG a nivel de chip. El IJTAG propone la inclusión de trayectorias jerárquicas dinámicas dentro de los registros de datos utilizando células jerárquicas dinámicas, tales como la célula conocida como la célula de Bits de Instrumento de Selección (SIB) . El uso de trayectorias jerárquicas dinámicas permite que porciones de la trayectoria de exploración se activen y desactiven según sea necesario. Por lo tanto, las trayectorias jerárquicas dinámicas que están habilitadas mediante el uso de células como SIB son un recurso de prueba valioso porque, como el número de elementos en la trayectoria de exploración es importante para determinar el tiempo de prueba, el uso cuidadoso de la jerarquía se puede utilizar para reducir el tiempo de prueba.

Como se describe en el estándar IEEE P1687 propuesto, la cadena de exploración es una cadena de exploración lineal y cada célula SIB que se inserta en la cadena de exploración se inserta para introducir jerarquía en la cadena de exploración. Por lo tanto, como la cadena de exploración es lineal, y a cada célula SIB incluida en la cadena de exploración lineal se debe acceder linealmente a través de la cadena de exploración para activar la jerarquía en la cadena de exploración, la longitud de la cadena de exploración determina directamente la cantidad de tiempo de acceso necesario para modificar y ejercer la jerarquía activa. Aunque esta limitación puede parecer insignificante en ejemplos en los que la cadena de exploración incluye sólo unas pocas células, esto puede ser una limitación importante en sistemas de la vida real, donde la cadena de exploración puede incluir cientos o incluso miles de células. Aunque el impacto de este problema puede reducirse mediante el uso de una programación precisa de procedimientos de prueba, este problema simplemente no puede evitarse por completo mediante el uso de la programación de procedimientos de prueba.

El documento US 4.872.169 describe un procedimiento para circuitería de pruebas. La circuitería de pruebas consiste en una serie de registros de desplazamiento o pestillos que forman una trayectoria de exploración en serie a través de un circuito lógico.

El documento JP 62093672 A describe un aparato lógico de tipo jerárquico. El aparato hace que sea posible realizar de manera eficiente el diagnóstico del problema de LSI sobre una base de jerarquía sin entrar en un circuito interno.

El documento US 6.587.981 B1 describe estructuras de trayectoria de exploración para circuitos integrados que contienen uno o más núcleos o niveles de sub-núcleos integrados dentro de los núcleos.

El documento US 2003/0131327 A1 describe un sistema y un procedimiento para probar un circuito integrado que tiene bloques de circuitos internos. Cada uno de los bloques de circuitos internos puede tener su propio bloque de circuito de prueba.

Sumario de la invención Se proporcionan aparatos, procedimientos y un programa de ordenador de sistema en chip de acuerdo con las reivindicaciones independientes.

Varias deficiencias en la técnica anterior se abordan mediante aparatos y procedimientos asociados para el control de una trayectoria de exploración de prueba de un sistema en chip usando una trayectoria de exploración de control separada del sistema en chip.

En una realización, un aparato incluye una trayectoria de exploración de prueba tiene una pluralidad de componentes de prueba incluyendo al menos un componente de prueba de habilitación de jerarquía, y una trayectoria de exploración de control que incluye al menos un componente de control acoplado a al menos un componente de prueba de habilitación de jerarquía de la trayectoria de exploración de prueba, en el que el al menos un componente de control está adaptado para controlar el al menos un componente de prueba de habilitación de jerarquía de una manera para modificar dinámicamente la trayectoria de exploración de prueba.

En una realización, un aparato incluye una trayectoria de exploración de prueba que tiene una pluralidad de componentes de prueba de habilitación no de jerarquía y al menos un componente de habilitación de jerarquía, y una trayectoria de exploración de control que incluye el al menos un componente de habilitación de jerarquía, en el que el al menos un componente de habilitación de jerarquía está adaptado para modificar dinámicamente la

trayectoria de exploración de prueba utilizando la trayectoria de exploración de control.

En una realización, un procedimiento incluye la aplicación de un flujo de bits de prueba a una trayectoria de exploración de prueba del sistema en chip, en el que la trayectoria de exploración de prueba soporta la jerarquía y aplica un flujo de bits de control a una trayectoria de exploración de control del sistema en chip, en el que el flujo de bits de control está adaptado para modificar dinámicamente la jerarquía de la trayectoria de exploración de prueba.

Breve descripción de los dibujos Las enseñanzas de la presente invención se pueden entender fácilmente considerando la siguiente descripción detallada en conjunción con los dibujos adjuntos, en los cuales:

La figura 1 representa un diagrama de bloques de alto nivel de un entorno de prueba;

La figura 2 representa un diagrama de bloques de alto nivel de un sistema en chip ejemplar adaptado para utilizarse en el entorno de prueba de la figura 1;

La figura 3 representa un diagrama de bloques de alto nivel de un sistema en chip ejemplar con una trayectoria de exploración jerárquica que incluye dos niveles jerárquicos controlados por un componente de habilitación de jerarquía;

La figura 4 representa un diagrama de bloques de alto nivel de un sistema en chip que incluye un componente de habilitación de jerarquía adaptado para modificar dinámicamente una trayectoria de exploración de un sistema en chip;

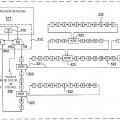

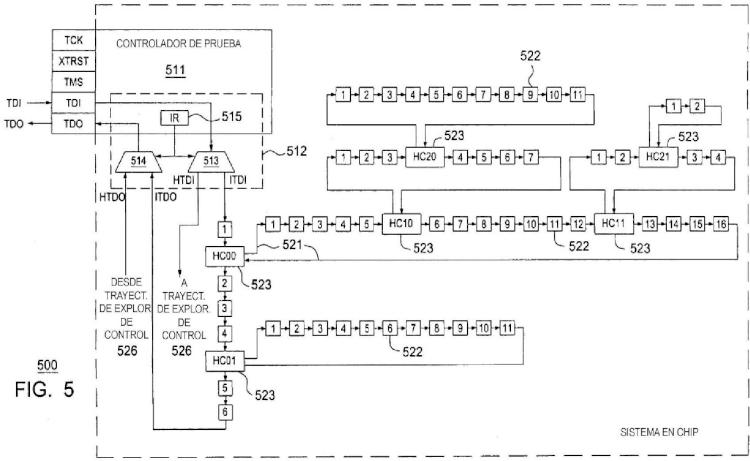

La figura 5 representa un diagrama de bloques de alto nivel de un sistema en chip jerárquico que incluye un controlador de pruebas y una trayectoria de exploración de prueba jerárquica;

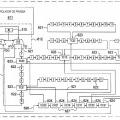

La figura 6 representa un diagrama de bloques de alto nivel de un sistema en chip que incluye una trayectoria de exploración de prueba y una trayectoria de exploración de control realizada usando componentes físicos separados;

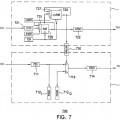

La figura 7 representa un diagrama de bloques de alto nivel de un componente de prueba de habilitación de jerarquía y un componente de control de jerarquía adaptado para su uso en la trayectoria de exploración de prueba y la trayectoria de exploración de control del sistema en chip de la figura 6;

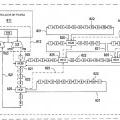

La figura 8 representa un diagrama de bloques de alto nivel de un sistema en chip que incluye una trayectoria de exploración de prueba y una trayectoria de exploración de control realizada usando componentes físicos combinados;

La figura 9 representa un diagrama de bloques de alto nivel de un componente de habilitación de jerarquía adaptado para soportar la trayectoria de exploración de prueba y la trayectoria de exploración de control del sistema en chip de la figura 8;

La figura 10 representa una realización de un procedimiento para probar un sistema en chip usando trayectorias de exploración de prueba y de control separadas;

La figura 11 representa un procedimiento ejemplar para probar un sistema en chip usando trayectorias de exploración de prueba y de control separadas;

La figura 12 representa un diagrama de bloques de alto nivel de un entorno de prueba en el que un sistema de prueba se utiliza para probar dos sistemas en chip;

La figura 13 representa un diagrama de bloques de alto nivel de un entorno de prueba en el que un sistema de prueba se utiliza para probar un sistema en chip que tiene integrado en el mismo un sistema en chip;

La figura 14 representa un diagrama de bloques de alto nivel de un entorno de prueba en el que un sistema de prueba se utiliza para probar un sistema... [Seguir leyendo]

Reivindicaciones:

1. Un aparato de sistema en chip (110, 500, 600, 800) , que comprende:

una trayectoria de exploración de prueba (521, 621, 821) que comprende una pluralidad de componentes de prueba (522) que incluyen al menos un componente de prueba de habilitación de jerarquía (523, 623, 825) ; y una trayectoria de exploración de control (526, 626, 823) que comprende al menos un componente de control (627, 825) , estando acoplado el al menos un componente de control a dicho al menos un componente de prueba de habilitación de jerarquía de la trayectoria de exploración de prueba; en el que el al menos un componente de control está adaptado para controlar el al menos un componente de prueba de habilitación de jerarquía de una manera para modificar dinámicamente la trayectoria de exploración de prueba, caracterizado porque la trayectoria de exploración de control es independiente de la trayectoria de exploración de prueba.

2. El aparato de la reivindicación 1, en el que la trayectoria de exploración de prueba incluye una jerarquía que tiene un primer nivel jerárquico y un segundo nivel jerárquico, en el que la modificación dinámica de la trayectoria de exploración de prueba comprende modificar dinámicamente la jerarquía de la trayectoria de exploración de prueba.

3. El aparato de la reivindicación 2, en el que la modificación dinámica de la jerarquía de la trayectoria de exploración de prueba comprende uno de seleccionar el segundo nivel jerárquico para activar el segundo nivel jerárquico y cancelar la selección del segundo nivel jerárquico para desactivar el segundo nivel jerárquico.

5. El aparato de la reivindicación 1, en el que el componente de control está adaptado para proporcionar una señal de control para controlar un elemento lógico del componente de prueba de habilitación de jerarquía. 7. El aparato de la reivindicación 6, en el que la trayectoria de exploración de prueba incluye una jerarquía que tiene un primer nivel jerárquico y un segundo nivel jerárquico, en el que la modificación dinámica de la trayectoria de exploración de prueba comprende modificar dinámicamente la jerarquía de la trayectoria de exploración de prueba. 8. El aparato de la reivindicación 6, en el que la trayectoria de exploración de prueba está adaptada para la propagación de un flujo de bits de prueba y la trayectoria de exploración de control está adaptada para la propagación de un flujo de bits de control. 9. El aparato de la reivindicación 6, en el que cada uno del al menos un componente de habilitación de jerarquía comprende un elemento de selección adaptado para seleccionar entre un flujo de bits de prueba y un flujo de bits de control. 10. Un procedimiento de prueba de un sistema en chip (110, 500, 600, 800) , que comprende: aplicar un flujo de bits de prueba a una trayectoria de exploración de prueba (521, 621, 821) de dicho sistema en chip, comprendiendo dicha trayectoria de exploración de prueba una pluralidad de componentes de prueba (522) que incluyen al menos un componente de prueba de habilitación de jerarquía (523, 623, 825) ; y aplicar de un flujo de bits de control a una trayectoria de exploración de control (526, 626, 823) de dicho sistema en chip, comprendiendo dicha trayectoria de exploración de control al menos un componente de 45 control (627, 825) , estando el al menos un componente de control acoplado a dicho al menos un componente de prueba de habilitación de jerarquía de la trayectoria de exploración de prueba, en el que el flujo de bits de control está adaptado para modificar dinámicamente la jerarquía de la trayectoria de exploración de prueba, caracterizado porque la trayectoria de exploración de control es independiente de la trayectoria de 50 exploración de prueba. 11. Un programa informático que tiene un código de programa para realizar el procedimiento de la reivindicación 10, cuando el programa informático se ejecuta en un ordenador o procesador. 12. Un medio de almacenamiento legible por ordenador que comprende instrucciones, cuando se ejecutan, para 55 hacer que una máquina realice el procedimiento de la reivindicación 10. 4. El aparato de la reivindicación 1, en el que la trayectoria de exploración de prueba está adaptada para la propagación de un flujo de bits de prueba, en el que la trayectoria de exploración de control está adaptada para la propagación de un flujo de bits de control.

6. El aparato de la reivindicación 1, en el que la trayectoria de exploración de control comprende el al menos un componente de habilitación de jerarquía, en el que el al menos un componente de habilitación de jerarquía está adaptado para modificar dinámicamente la trayectoria de exploración de prueba utilizando la trayectoria de exploración de control.

Patentes similares o relacionadas:

Dispositivo de protección contra fallas en circuitos de árbol de reloj, del 10 de Febrero de 2016, de Winbond Electronics Corp: Un circuito integrado "CI", que comprende:

Un circuito de árbol de reloj configurado para distribuir una señal de reloj en el circuito […]

Dispositivo de protección contra fallas en circuitos de árbol de reloj, del 10 de Febrero de 2016, de Winbond Electronics Corp: Un circuito integrado "CI", que comprende:

Un circuito de árbol de reloj configurado para distribuir una señal de reloj en el circuito […]

DISPOSITIVO Y PROCEDIMIENTO PARA CREAR UNA FIRMA., del 16 de Noviembre de 2006, de SIEMENS AKTIENGESELLSCHAFT: Dispositivo para crear una firma, en donde se ha previsto una cantidad precalculada de registros de desplazamiento , en los que se depositan […]

SISTEMA Y PROCEDIMIENTO PARA PPREPROGRAMAR LA MEMORIA DE UN DISPOSITIVO ELECTRONICO., del 16 de Julio de 2006, de QUALCOMM INCORPORATED: Procedimiento para programar en paralelo la memoria de un dispositivo electrónico con un código de prueba y un código de sistema antes de […]

SISTEMA DIGITAL Y METODO DE DETECCION DE ERRORES DEL MISMO., del 1 de Junio de 2006, de KONINKLIJKE PHILIPS ELECTRONICS N.V.: Sistema digital para procesar un vector (VEn_p) digital de entrada, que comprende p bits (E1, E2, ..., Ep), para proporcionar un vector (VSa_q) digital […]

METODO PARA ALMACENAR PROPIEDADES DE REGISTRO EN UNA ESTRUCTURA DE DATOS Y ESTRUCTURA DE DATOS RELACIONADA., del 1 de Junio de 2006, de ALCATEL: Método para almacenar propiedades de registro de un dispositivo hardware (ASIC1, ASIC2, ASIC3, ASIC4) que tiene memoria heterogénea, en una estructura de datos, estando […]

PROCEDIMIENTO DE PRUEBA DE RADIOFRECUENCIA SIN HILOS DE CIRCUITOS INTEGRADOS Y OBLEAS., del 16 de Marzo de 2006, de THE GOVERNORS OF THE UNIVERSITY OF ALBERTA: Aparato para probar un circuito integrado sobre una oblea que comprende: a) un circuito de prueba formado sobre la oblea con el circuito […]

DISPOSICION PARA VERIFICACION JTAG., del 16 de Septiembre de 2005, de PATRIA FINAVITEC OY: Un sistema de verificación JTAG que comprende un equipo de prueba JTAG (TS) y un dispositivo en fase de prueba (DUT) compatible con el JTAG dispuesto para formar una conexión […]

COMPOSICIONES DE TRAZAS DE DATOS PARA UN CIRCUITO INTEGRADO DE MEMORIAS MULTIPLES, del 1 de Marzo de 2009, de QUALCOMM INCORPORATED: Un circuito integrado que comprende: una pluralidad de memorias (126a, 126b); y un módulo de traza operativo para formar paquetes de trazas de datos, […]

COMPOSICIONES DE TRAZAS DE DATOS PARA UN CIRCUITO INTEGRADO DE MEMORIAS MULTIPLES, del 1 de Marzo de 2009, de QUALCOMM INCORPORATED: Un circuito integrado que comprende: una pluralidad de memorias (126a, 126b); y un módulo de traza operativo para formar paquetes de trazas de datos, […]