Aparato para predecir direcciones objetivo de conexión múltiples.

Un aparato en un microprocesador (100) para predecir una dirección objetivo para un número variable de instrucciones de conexión en una línea en memoria caché captada de una memoria caché de instrucciones (104) en una dirección de captación,

estando el aparato caracterizado por:

M memorias caché asociativas (208) de un conjunto de N vías, teniendo cada una una entrada de índices acoplada para recibir una parte de la dirección de captación de la memoria caché de instrucciones, en el que dicho índice selecciona una de una pluralidad de grupos de MxN entradas, comprendiendo dicho grupo una entrada en cada vía de cada una de dichas M memorias caché (208), en el que cada una de dichas entradas está configurada para colocar en memoria caché una dirección objetivo de una instrucción de conexión previamente ejecutada, en el que dicha M es mayor que 1; y una lógica de sustitución, acoplada a dichas M memorias caché (208), configurada para seleccionar una de dichas entradas en respuesta a dos resoluciones de una instrucción de conexión, de forma que durante el funcionamiento del microprocesador:

a) para un primer subconjunto de dicha pluralidad de grupos dichas MxN entradas están colocando en memoria caché direcciones objetivo para una instrucción de conexión en cada una de las MxN líneas en memoria caché diferentes para obtener una asociatividad de grupos de MxN vías, y

b) para un segundo subconjunto de dicha pluralidad de grupos dichas MxN entradas están colocando en memoria caché direcciones objetivo para una instrucción de conexión en cada una de (MxN-1) líneas en memoria caché diferentes y dos instrucciones de conexión en una línea en memoria caché diferente MxN-ésima para obtener de forma efectiva una asociatividad de grupos de (MxN-1) vías.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E05254882.

Solicitante: VIA TECHNOLOGIES, INC..

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: 8F, NO. 535, CHUNG-CHENG RD, HSIN-TIEN TAIPEI 231, TAIWAN TAIWAN.

Inventor/es: HENRY,G. GLENN, McDonald,Thomas C.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F9/00 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10).

- G06F9/32 G06F […] › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Formación de la dirección de la instrucción siguiente, p. ej. por incremento del contador de instrucción (G06F 9/38 tiene prioridad).

- G06F9/38 G06F 9/00 […] › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

PDF original: ES-2378236_T3.pdf

Fragmento de la descripción:

Aparato para predecir direcciones objetivo de conexión múltiples.

REFERENCIA CRUZADA CON APLICACIÓN O APLICACIONES RELACIONADAS

Esta solicitud reivindica la prioridad basada en la Solicitud Provisional, Serie Nº 60/598.868, presentada el 4 de agosto de 2004 titulada MEMORIA CACHÉ DE DIRECCIONES OBJETIVO DE CONEXIÓN CON UNA EFICIENCIAMEJORADA PARA ENTREGAR DIRECCIONES OBJETIVO MÚLTIPLES POR ACCESO.

Esta solicitud es una continuación en parte (CIP) de las siguientes Solicitudes de Patente de EEUU no provisionales en trámite, las cuales están aquí incorporadas por referencia en su totalidad para todos los fines:

Serie Nº (Registro Nº ) Fecha de presentación Título 09/849736 (CNTR 2021) 5/4/2001 MICROPROCESADOR CON MEMORIA CACHÉ DE DIRECCIONES OBJETIVO DE CONEXIÓN PARA REALIZAR UNA CONEXIÓN ESPECULATIVA 10/978802 (CNTR 2023-C1) 11/1/2004 PREDICTOR DE DIRECCIONES DE CONEXIÓN HÍBRIDA ESPECULATIVA 10/978812 (CNTR 2063-C1) 11/1/2004 APARATO Y MÉTODO PARA LA SUSTITUCIÓN DE DIRECCIONES OBJETIVO EN LA MEMORIA CACHÉ DE DIRECCIONES OBJETIVO DE CONEXIÓN ESPECULATIVA 10/632226 (CNTR 2140) 7/31/2003 APARATO Y MÉTODO PARA LA ACTUALIZACIÓN EFICIENTE DE MEMORIA CACHÉ DE DIRECCIONES OBJETIVO DE CONEXIÓNLa Solicitud de Patente de EEUU pendiente, Serie Nº 10/978802 (CNTR 2023-C1) es una continuación de la Patente de EEUU Nº 6.886.093 presentada el 4 de mayo de 2001; la Solicitud de Patente de EEUU pendiente, Serie Nº 10/978812 (CNTR 2063-C1) es una continuación de la Patente de EEUU Nº 6.895.498 presentada el 4 de mayo de 2001; la Solicitud de Patente de EEUU pendiente, Serie Nº 10/632226 (CNTR 2140) reivindica la prioridad de la Solicitud Provisional de EEUU Serie Nº 60/440065 presentada el 14 de abril de 2003.

CAMPO DEL INVENTO El presente invento se refiere en general al campo de la predicción de conexión en microprocesadores, y particularmente a memorias caché de direcciones objetivo de conexión.

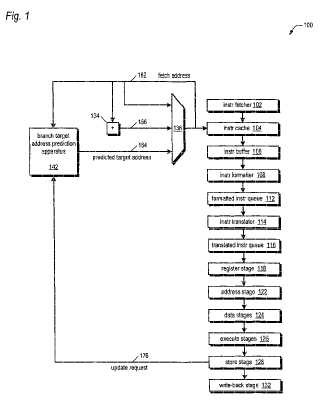

ANTECEDENTES DEL INVENTO Muchos microprocesadores canalizados con un modem incluyen una memoria caché de direcciones objetivo de conexión (BTAC) que coloca en memoria caché las direcciones de instrucciones de conexión previamente ejecutadas. Cuando una línea en memoria caché es captada de la memoria caché de instrucciones del microprocesador, la dirección captada es proporcionada a la BATC, y dicha BATC usa la dirección de captación para predecir si existe una instrucción de conexión presente en la línea en memoria caché y si la BATC contiene una dirección objetivo válida para la instrucción de conexión. Si se predice que la instrucción ha de ser tomada, el procesador se conecta con la dirección objetivo válida suministrada por la BATC. Puesto que cada línea en memoria caché puede almacenar múltiples instrucciones, la línea en memoria caché de instrucciones puede contener más de una instrucción de conexión. Por lo tanto, algunas BTACs estáticas dedican un almacenamiento para colocar en memoria caché dos direcciones objetivo por línea en memoria caché. Esto permite que la BTAC prediga de forma más precisa el desarrollo del programa ya que es posible que una de las instrucciones de conexión en la línea en memoria caché será tomada y la otra no será tomada.

En las BTACs convencionales el almacenaje de las dos direcciones objetivo está fijado en la BTAC. Esto es, el espacio está dedicado estática e independientemente de si están presentes dos instrucciones de conexión en la línea en memoria caché o sólo está presente una instrucción de conexión en la línea en memoria caché. De hecho, en una BTAC convencional que está integrada en la instrucción coloca en memoria caché el espacio está dedicado estáticamente incluso si en la línea en memoria caché están presentes cero instrucciones de conexión. No obstante, se ha observado que sólo aproximadamente el 20% de las líneas en memoria caché que contienen una instrucción de conexión contienen dos instrucciones de conexión. Por lo tanto, el espacio extra en la BTAC dedicado estáticamente para la segunda dirección objetivo es consumido por el 80% de las líneas en memoria caché. Por ejemplo, en una BTAC que es una memoria caché asociativa de un conjunto de dos vías que estáticamente dedica el almacenamiento para dos direcciones objetivo por entrada, puesto que sólo aproximadamente el 20% de las líneas en memoria caché incluye dos o más instrucciones de conexión, solamente se usa aproximadamente el 60% del espacio de almacenamiento de direcciones objetivo para almacenar direcciones objetivo válidas.

El documento US 5.802.602 describe un sistema de predicción de conexión que usa un conjunto de N vías de memoria caché asociativa.

Por lo tanto, lo que se necesita es un esquema de espacio más eficiente en cuanto a espacio para predecir instrucciones de conexión múltiples en una línea en memoria caché captada.

BREVE SUMARIO DE INTENCIÓN El presente invento proporciona un aparato de predicción de conexión que determina dinámicamente la asociatividad de un grupo de entradas seleccionadas por un índice de direcciones de captación dado que depende del número de instrucciones de conexión presente en las líneas en memoria caché especificadas por el índice, por lo que se disfruta de una mayor asociatividad de índices con sólo una única instrucción de conexión y menos asociatividad de índices con múltiples instrucciones de conexión.

En un aspecto, el presente invento proporciona un aparato en un microprocesador para predecir una dirección objetivo para un número variable de instrucciones de conexión en cada línea en memoria caché captada de una memoria caché de instrucciones en una dirección de captación. El aparato incluye unas memorias caché asociativas de los conjuntos de dos vías primero y segundo, teniendo cada uno una entrada de índice acoplada para recibir una parte de la dirección de captación en memoria caché de la instrucción. El índice selecciona uno de una pluralidad de grupos de cuatro entradas. Cada grupo tiene una entrada en cada vía de cada una de las memorias en memoria caché primera y segunda. Cada una de las entradas está configurada para colocar en memoria caché una dirección objetivo de una instrucción de conexión previamente ejecutada. El aparato incluye también la lógica de sustitución, acoplada con las memorias caché primera y segunda, configurada para seleccionar la sustitución de una de las entradas, en respuesta a la resolución de una instrucción de conexión, de forma que durante el funcionamiento del microprocesador: a) para un primer subconjunto de la pluralidad de grupos, las cuatro entradas están colocando en memoria caché direcciones objetivo de una instrucción de conexión en cada una de cuatro líneas en memoria caché diferentes, para obtener una asociatividad de grupos de cuatro vías; y b) de un segundo subconjunto de la pluralidad de grupos, las cuatro entradas están colocando en memoria caché direcciones objetivo de una instrucción de conexión en cada una de dos líneas en memoria caché diferentes y dos instrucciones de conexión en una tercera línea en memoria caché diferente para obtener una asociatividad de grupos de tres vías.

En otro aspecto el presente invento proporciona un método en un microprocesador para predecir una dirección objetivo para un número variable de instrucciones de conexión en una línea en memoria caché captada de una memoria caché de instrucciones en una dirección de captación. El método incluye proporcionar un índice de las memorias caché asociativas de los conjuntos de dos vías primero y segundo para seleccionar uno de una pluralidad de grupos de cuatro entradas. Cada grupo incluye una entrada en cada vía de cada una de las memorias caché primera y segunda. Cada una de las entradas coloca en memoria caché una dirección objetivo de una instrucción de conexión previamente ejecutada. El índice es una parte de la dirección de captación en memoria caché de la instrucción. El método incluye también seleccionar para sustitución, en respuesta a la resolución de una instrucción de conexión, una de las entradas, de forma que durante el funcionamiento del microprocesador: a) para un primer subconjunto de la pluralidad de grupos, las cuatro entradas están colocando en memoria caché direcciones objetivo de una instrucción de conexión en cada una de cuatro líneas en memoria caché diferentes para obtener una asociatividad de grupos de cuatro vías; y b) para un segundo subconjunto de la pluralidad de grupos las cuatro entradas están colocando en memoria caché direcciones objetivo... [Seguir leyendo]

Reivindicaciones:

1. Un aparato en un microprocesador (100) para predecir una dirección objetivo para un número variable de instrucciones de conexión en una línea en memoria caché captada de una memoria caché de instrucciones (104) en una dirección de captación, estando el aparato caracterizado por:

M memorias caché asociativas (208) de un conjunto de N vías, teniendo cada una una entrada de índices acoplada para recibir una parte de la dirección de captación de la memoria caché de instrucciones, en el que dicho índice selecciona una de una pluralidad de grupos de MxN entradas, comprendiendo dicho grupo una entrada en cada vía de cada una de dichas M memorias caché (208) , en el que cada una de dichas entradas está configurada para colocar en memoria caché una dirección objetivo de una instrucción de conexión previamente ejecutada, en el que dicha M es mayor que 1; y una lógica de sustitución, acoplada a dichas M memorias caché (208) , configurada para seleccionar una de dichas entradas en respuesta a dos resoluciones de una instrucción de conexión, de forma que durante el funcionamiento del microprocesador:

a) para un primer subconjunto de dicha pluralidad de grupos dichas MxN entradas están colocando en memoria caché direcciones objetivo para una instrucción de conexión en cada una de las MxN líneas en memoria caché diferentes para obtener una asociatividad de grupos de MxN vías, y b) para un segundo subconjunto de dicha pluralidad de grupos dichas MxN entradas están colocando en memoria caché direcciones objetivo para una instrucción de conexión en cada una de (MxN-1) líneas en memoria caché diferentes y dos instrucciones de conexión en una línea en memoria caché diferente MxN-ésima para obtener de forma efectiva una asociatividad de grupos de (MxN-1) vías.

2. El aparato mencionado en la reivindicación 1, en el que para dicho segundo subconjunto de dicha pluralidad de grupos, si la dirección de captación de memorias caché de instrucciones acierta en dos de dichas memorias caché, dichas M memorias caché están configuradas para proporcionar dichas direcciones objetivo de dichas dos instrucciones de conexión en dicha línea en memoria caché MxN-ésima.

3. El aparato mencionado en la reivindicación 2, que además comprende:

un multiplexor de selección de lado acoplado a dichas M memorias caché, configurado para seleccionar una de dichas direcciones objetivo de dichas dos instrucciones de conexión en dicha tercera línea en memoria caché basándose en una situación de cada una de dichas dos instrucciones de conexión dentro de dicha línea en memoria caché MxN-ésima relativa a un indicador de instrucción del microprocesador.

4. El aparato mencionado en la reivindicación 3, en el que dicho multiplexor de selección de lado está configurado para seleccionar una de dichas direcciones objetivo de una primera válida, tomada, vista de dichas dos instrucciones de conexión relativas a dicho indicador de instrucción.

5. El aparato mencionado en la reivindicación 1, en el que dicha lógica de sustitución está además configurada para seleccionar para sustitución una de dichas entradas en respuesta a la resolución de una instrucción de conexión, de forma que durante el funcionamiento del microprocesador:

c) para un tercer subconjunto de dicha pluralidad de grupos, dichas MxN entradas están colocando en memoria caché direcciones objetivo de una instrucción de conexión en cada una de (MxN-2) líneas en memoria caché diferentes y dos instrucciones de conexión en cada una de dos líneas en memoria caché diferentes para obtener una asociatividad de grupos de (MxN-2) vías.

6. El aparato mencionado en la reivindicación 1, en el que dicha lógica de sustitución está además configurada para seleccionar para sustitución una de dichas entradas en respuesta a la resolución de una instrucción de conexión, de forma que durante el funcionamiento del microprocesador:

c) para un tercer subconjunto de dicha pluralidad de grupos, dichas MxN entradas están colocando en memoria caché direcciones objetivo de M instrucciones de conexión en cada una de N líneas en memoria caché diferentes para obtener una asociatividad de grupos de N vías.

7. El aparato mencionado en la reivindicación 1, en el que dicha M es 2 y dicha N es 2.

8. Un método en un microprocesador (100) para predecir una dirección objetivo para un número variable de instrucciones de conexión en una línea en memoria caché captada de una memoria caché de instrucciones (104) en una dirección de captación, estando el aparato caracterizado por los pasos de:

proporcionar un índice a M memorias caché asociativas (208) de conjuntos de N vías para seleccionar una de la pluralidad de grupos de MxN entradas, comprendiendo cada grupo una entrada en cada vía de cada una de las M memorias caché (208) , colocando en memoria caché cada una de las entradas una dirección

objetivo de una instrucción de conexión previamente ejecutada, siendo el índice una parte de la dirección de captación de la memoria caché de instrucciones, en el que M es mayor que 1, y seleccionando para sustitución, en respuesta a la resolución de una instrucción de conexión, una de las entradas de forma que durante el funcionamiento del microprocesador:

a) para un primer subconjunto de la pluralidad de grupos las MxN entradas están colocando en memoria caché direcciones objetivo para una instrucción de conexión en cada una de las MxN líneas en memoria caché diferentes para obtener una asociatividad de grupos de MxN vías, y b) para un segundo subconjunto de dicha pluralidad de grupos, las MxN entradas están colocando en memoria caché direcciones objetivo para una instrucción de conexión en cada una de las (MxN-1) líneas en memoria caché diferentes y dos instrucciones de conexión en una línea en memoria caché diferente MxN-ésima para obtener de forma efectiva una asociatividad de grupos de (MxN-1) vías.

9. El método mencionado en la reivindicación 8, que además comprende:

para el segundo subconjunto de la pluralidad de grupos, determinar si la dirección de captación en memoria caché de instrucciones acierta en dos de las M memorias caché; proporcionar por cada una de las dos o las M memorias caché las direcciones objetivo de las dos instrucciones de conexión en la línea en memoria caché MxN-ésima; y seleccionar una de las direcciones objetivo de las dos instrucciones de conexión en la memoria caché MxNésima basándose en una situación de cada una de las dos instrucciones de conexión dentro de la línea en memoria caché MxN-ésima uno y la correspondiente dos un indicador de instrucción del microprocesador, en el que dicha selección de una de las direcciones objetivo comprende seleccionar una de las direcciones objetivo de una primera válida, tomada, vista una de las dos instrucciones de conexión relativa al indicador de instrucción.

10. El método mencionado en la reivindicación 8, que además comprende:

almacenar una información de sustitución asociada con cada uno de la pluralidad de grupos para uso en dicha selección para sustitución de una de las entradas, en respuesta a la resolución de la instrucción de conexión.

11. El método mencionado en la reivindicación 10, en el que si la instrucción de conexión resuelta no tiene su dirección objetivo ya en memoria caché en las M memorias caché, y si la dirección de captación de la instrucción de conexión resuelta no acierta en al menos una de las M memorias caché, dicha selección para sustitución comprende la selección para sustituir de una de las vías de al menos una de las M memorias caché.

12. El método mencionado en la reivindicación 11, en el que la información de sustitución comprende, para cada uno de los M conjuntos de cada grupo, una indicación de cuál de las N vías del conjunto fue usada recientemente, en el que dicha selección de sustitución comprende seleccionar para sustitución la última vía recientemente usada.

13. El método mencionado en la reivindicación 10, en el que la información de sustitución comprende una indicación de cuál de las M memorias caché fue la menos usada recientemente, en el que si la instrucción de conexión resuelta no tiene su dirección objetivo ya colocada en memoria caché en las M memorias caché, y si la dirección de captación de la instrucción de conexión resuelta acierta en todas las M memorias caché, dicha selección para sustitución comprende la selección para sustitución de la menos recientemente usada de las M memorias caché.

14. El método mencionado en la reivindicación 10, en el que la información de sustitución comprende una indicación de cuál de las M memorias caché fue la menos usada recientemente, en el que si la instrucción de conexión resuelta no tiene su dirección objetivo ya colocada en memoria caché en las M memorias caché, y si la dirección de captación de la instrucción de conexión resuelta no acierta en ninguna de las M memorias caché, dicha selección para sustitución comprende la selección para sustitución de la menos recientemente usada de las M memorias caché.

15. El método mencionado en la reivindicación 8, en el que M es 2 y N es 2.

Patentes similares o relacionadas:

Transmisión de datos con tráfico intenso, del 17 de Febrero de 2020, de Mueller International, LLC: Procedimiento de recepción de datos mediante un nodo colector, que comprende: escuchar, con el nodo colector, durante un período de escucha, una […]

Sistemas y procedimientos para la distribución de datos dentro de una red interconectada, del 5 de Junio de 2019, de Mueller International, LLC: Un sistema que comprende: un proveedor de servicios públicos configurado para proporcionar servicios de servicios públicos a una […]

Sistemas y procedimientos de virtualización de dispositivos bimodales de dispositivos basados en hardware reales e idealizados, del 28 de Febrero de 2018, de Microsoft Technology Licensing, LLC: Un sistema informático, comprendiendo dicho sistema informático un sistema operativo de invitado , un dispositivo virtual bimodal y un sistema […]

Dispositivo de registro de datos adaptado para combinar dosis, del 27 de Diciembre de 2017, de NOVO NORDISK A/S: Un dispositivo de registro adaptado para ser unido de manera que se pueda separar a un dispositivo de administración de medicamento, comprendiendo […]

Método para configurar la funcionalidad de control remoto de un dispositivo portátil, del 4 de Octubre de 2017, de UNIVERSAL ELECTRONICS, INC.: Un método para seleccionar un conjunto de códigos para su uso en la configuración de un dispositivo portátil para comandar operaciones funcionales de un aparato , […]

SISTEMA INTEGRADO PARA PROCEDIMIENTO DE BLOQUEO, del 8 de Septiembre de 2017, de CÁDIZ FLORES, Julio Enrique: La presente invención se refiere a un sistema y un procedimiento integrados para el bloqueo de equipos, que entrega una mayor seguridad, confiabilidad y eficiencia […]

SISTEMA MULTISENSOR PARA REHABILITACIÓN E INTERACCIÓN DE PERSONAS CON DISCAPACIDAD, del 13 de Abril de 2017, de UNIVERSIDAD DE ALICANTE: Sistema multisensor para rehabilitación e interacción de personas con discapacidad, tanto motora, como cognitiva. El sistema permite la realización de terapias utilizando […]

SISTEMA DE CONTROL PARA INSTRUMENTOS MUSICALES, del 21 de Febrero de 2017, de CARCELLER GALLARDO, Roser: 1. Sistema de control para instrumentos musicales, caracterizado por comprender, al menos: - una unidad electrónica , acoplable a la funda […]