PROCEDIMIENTO PARA LA VERIFICACION DE UN NUCLEO DE ORDENADOR DE UN MICROPROCESADOR O DE UN MICRO CONTROLADOR.

Procedimiento para la creación de una prueba automática (7) para la verificación de la función correcta de un núcleo de ordenador (36) de un microprocesador (30) o de un microcontrolador,

en el que el núcleo del ordenador (36) comprende varias puertas con varios transistores, respectivamente, en el que durante una ejecución correcta de un programa de ordenador (3) en el microprocesador (30) o microcontrolador se ejecuta cíclicamente una prueba automática (7) y en el marco de la prueba automática (7) se verifica la función correcta de puertas del núcleo del ordenador, caracterizado porque se verifican al menos aquellas puertas del núcleo del ordenador (36), cuyo estado tiene repercusiones sobre la ejecución correcta del programa de ordenador (3) en el microprocesador (30) o microcontrolador, durante la ejecución de la prueba automática (7), y se crea en este caso la prueba automática (4), de tal manera que - se crea (11) un proyecto de la prueba automática (7) para el núcleo del ordenador (36); - se verifica si el estado de aquellas puertas del núcleo del ordenador (36), que no son verificadas por el proyecto de la prueba automática (7) durante una ejecución, tiene repercusiones sobre el desarrollo correcto del programa de ordenador (3) sobre el microprocesador (30) o microcontrolador (14); - en el caso de que el estado de al menos una puerta del núcleo del ordenador, que no es verificado por el proyecto de la prueba automática (7) durante una operación, tenga repercusiones sobre el desarrollo correcto del programa de ordenador (3) en el microprocesador (30) o microcontrolador, se crea la prueba automática (7) acabada, siendo ampliado el proyecto de la prueba automática (7) de tal forma que se verifican adicionalmente al menos aquellas puertas del núcleo del ordenador (36), que no han sido verificadas por el proyecto de la prueba automática (7) y cuyo estado tiene repercusiones sobre el desarrollo correcto del programa de ordenador (3) sobre el microprocesador (30) o microcontrolador, y - en el caso de que el estado de aquellas puertas del núcleo del ordenador (36), que no son verificadas por el proyecto de la prueba automática (7) durante una ejecución, no tenga repercusiones sobre el desarrollo correcto del programa de ordenador (3) en el microprocesador (30) o microcontrolador, se utiliza (20) el proyecto de la prueba automática (7) como prueba automática acabada (7).

Tipo: Resumen de patente/invención.

Solicitante: ROBERT BOSCH GMBH.

Nacionalidad solicitante: Alemania.

Dirección: POSTFACH 30 02 20,70442 STUTTGART.

Inventor/es: MATTERN, KLAUS-PETER, HERING, MICHAEL, HARTER, WERNER.

Fecha de Publicación: .

Fecha Solicitud PCT: 30 de Julio de 2002.

Clasificación Internacional de Patentes:

- G06F11/22 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Detección o localización de hardware defectuoso efectuando pruebas durante las operaciones de espera (standby) o durante los tiempos muertos, p. ej. pruebas de arranque.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Oficina Europea de Patentes, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania, Armenia, Azerbayán, Bielorusia, Ghana, Gambia, Kenya, Kirguistán, Kazajstán, Lesotho, República del Moldova, Malawi, Mozambique, Federación de Rusia, Sudán, Sierra Leona, Tayikistán, Turkmenistán, República Unida de Tanzania, Uganda, Zimbabwe, Burkina Faso, Benin, República Centroafricana, Congo, Costa de Marfil, Camerún, Gabón, Guinea, Malí, Mauritania, Niger, Senegal, Chad, Togo, Zambia, Organización Regional Africana de la Propiedad Industrial, Swazilandia, Guinea-Bissau, Guinea Ecuatorial, Organización Africana de la Propiedad Intelectual, Organización Eurasiática de Patentes.

Patentes similares o relacionadas:

Vigilancia a distancia de un sistema de procesamiento de datos mediante una red de comunicaciones, del 30 de Octubre de 2018, de Accenture Global Services Limited: Un sistema de procesamiento de datos a distancia que comprende: un receptor de datos para recibir un mensaje de datos; una […]

uso de toma de huellas digitales de potencia (pfp) para monitorizar la integridad y potenciar la seguridad de sistemas informáticos, del 22 de Febrero de 2017, de VIRGINIA TECH INTELLECTUAL PROPERTIES, INC.: Método para realizar una estimación de integridad en tiempo real de ejecución de una rutina en una plataforma de procesamiento informático, que comprende: (a) […]

SISTEMA Y PROCEDIMIENTO PARA DETECTAR UN DEFECTO EN LAS INTERCONEXIONES DE GRAN LONGITUD DE UN CIRCUITO DIGITAL AVANZADO, del 7 de Mayo de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Sistema y procedimiento para detectar un defecto en las interconexiones de gran longitud de un circuito digital avanzado.

La invención […]

SISTEMA Y PROCEDIMIENTO PARA DETECTAR UN DEFECTO EN LAS INTERCONEXIONES DE GRAN LONGITUD DE UN CIRCUITO DIGITAL AVANZADO, del 7 de Mayo de 2012, de UNIVERSITAT POLITECNICA DE CATALUNYA: Sistema y procedimiento para detectar un defecto en las interconexiones de gran longitud de un circuito digital avanzado.

La invención […]

DISPOSITIVO DE IMPRESION, METODO DE DIAGNOSTICO PARA DISPOSITIVO DE IMPRESION Y PROGRAMA DE DIAGNOSTICO PARA DISPOSITIVO DE IMPRESION., del 1 de Junio de 2007, de SEIKO EPSON CORPORATION: Una impresora adaptada a usar una pluralidad de canales (1ch, ....8ch) para realizar la comunicación inalámbrica, que comprende; unos medios de salida […]

SISTEMA Y METODO PARA EL DIAGNOSTICO EN SERVICIO DEL SOFTWARE DE UN SISTEMA DE DISPOSITIVO DE COMUNICACIONES SIN CABLES., del 16 de Diciembre de 2006, de KYOCERA WIRELESS CORPORATION: Método para diagnóstico en servicio de software de sistema en un dispositivo de comunicaciones sin cables, cuyo método comprende: ejecutar el software del sistema […]

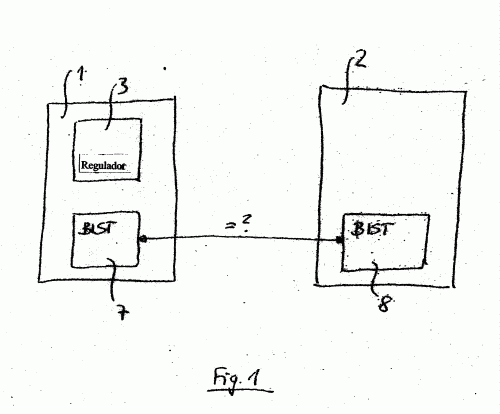

PRUEBA AUTOMATICA INTEGRADA JERARQUICA., del 1 de Diciembre de 2006, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un aparato para proporcionar autocomprobación integrada jerárquica para un sistema con chip, comprendiendo dicho aparato: un controlador BIST […]

APARATO Y METODO PARA RECUPERAR DATOS A DISTANCIA., del 16 de Noviembre de 2004, de ONTRACK DATA INTERNATIONAL, INC.: La invención se refiere a un aparato y a un procedimiento para recuperar a distancia datos inaccesibles sobre dispositivos informáticos de almacenamiento. El […]

DETECTOR DE CONGELACION DE IMAGEN, del 3 de Junio de 2009, de JAKOB HATTELAND DISPLAY AS: Procedimiento para identificar una situación de congelación de imagen en una pantalla, comprendiendo el procedimiento: #- añadir una firma electrónica en una señal alimentada […]

DETECTOR DE CONGELACION DE IMAGEN, del 3 de Junio de 2009, de JAKOB HATTELAND DISPLAY AS: Procedimiento para identificar una situación de congelación de imagen en una pantalla, comprendiendo el procedimiento: #- añadir una firma electrónica en una señal alimentada […]