Procedimiento para formar una imagen conductora sobre una superficie no conductora.

Procedimiento para formar una capa conductora sobre una superficie,

que comprende realizar las siguientes etapas en orden:

activar por lo menos una parte de una superficie del sustrato no conductora;

aplicar un campo magnético a la superficie;

depositar un complejo de coordinación metálico sobre por lo menos una parte de la parte activada de la superficie;

retirar el campo magnético;

exponer el complejo de coordinación metálico a una radiación electromagnética;

reducir el complejo de coordinación metálico a un metal elemental;

eliminar el complejo de coordinación metálico no reducido de la superficie;

secar la superficie; y

depositar un material conductor sobre la superficie.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2012/051193.

Solicitante: Earthone Circuit Technologies Corporation.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 2236 Rutherford Road, Suite 119 Carlsbad, CA 92008 ESTADOS UNIDOS DE AMERICA.

Inventor/es: WISMANN,WILLIAM.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H01L21/288 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 21/00 Procedimientos o aparatos especialmente adaptados para la fabricación o el tratamiento de dispositivos semiconductores o de dispositivos de estado sólido, o bien de sus partes constitutivas. › a partir de un líquido, p. ej. depósito electrolítico.

- H01L21/768 H01L 21/00 […] › Fijación de interconexiones que sirvan para conducir la corriente entre componentes separados en el interior de un dispositivo.

- H05K3/10 H […] › H05 TECNICAS ELECTRICAS NO PREVISTAS EN OTRO LUGAR. › H05K CIRCUITOS IMPRESOS; ENCAPSULADOS O DETALLES DE LA CONSTRUCCIÓN DE APARATOS ELECTRICOS; FABRICACION DE CONJUNTOS DE COMPONENTES ELECTRICOS. › H05K 3/00 Aparatos o procedimientos para la fabricación de circuitos impresos. › en los cuales el material conductor es aplicado al soporte aislante de manera que forme el diseño de conductor deseado.

- H05K3/18 H05K 3/00 […] › utilizando técnicas de precipitación para aplicar el material conductor.

- H05K3/38 H05K 3/00 […] › Mejoramiento de la adherencia entre el sustrato aislante y el metal.

PDF original: ES-2548415_T3.pdf

Fragmento de la descripción:

Procedimiento para formar una imagen conductora sobre una superficie no conductora.

Campo La presente invención se refiere al campo de la fabricación de dispositivos electrónicos.

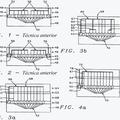

Antecedentes Las imágenes conductoras sobre superficies no conductoras o dieléctricas se encuentran por todos lados en el mundo actual en el que la tecnología lo mueve todo. Tal vez el ejemplo más ampliamente conocido de las mismas son los circuitos integrados que se encuentran en prácticamente todos los dispositivos electrónicos. Los circuitos integrados son resultado de una secuencia de etapas de procesamiento fotográficas y químicas mediante las cuales se crean gradualmente los circuitos sobre un sustrato dieléctrico tal como una oblea de silicio.

Una oblea típica está compuesta por silicio extremadamente puro que se hace crecer dando lugar a lingotes cilíndricos monocristalinos, denominados monocristales, que presentan hasta 300 mm de diámetro. Los monocristales se rebanan dando lugar a obleas de aproximadamente 0, 75 mm de grosor y se pulen para obtener una superficie plana muy lisa.

La formación de un circuito sobre una oblea requiere numerosas etapas que pueden clasificarse en dos partes principales: procesamiento de fabricación inicial (FEOL) y procesamiento de fabricación final (BEOL) .

El procesamiento FEOL se refiere a la formación de circuitos directamente en el silicio. La oblea en bruto se somete en primer lugar a epitaxia, el crecimiento de cristales de silicio ultrapuro sobre la oblea, en el que los cristales imitan la orientación del sustrato.

Tras la epitaxia, la ingeniería de superficies inicial generalmente consiste en las etapas de crecimiento del dieléctrico de puerta, tradicionalmente dióxido de silicio (SiO2) , la estructuración de la puerta, la estructuración de las regiones fuente y de drenaje, y la posterior implantación o difusión de dopantes para obtener las propiedades eléctricas complementarias deseadas. En dispositivos de memoria de acceso aleatorio dinámico (DRAM) , también se fabrican en este momento los condensadores de almacenamiento, normalmente apilados por encima del transistor de acceso.

Una vez creados los diversos dispositivos semiconductores, deben interconectarse para formar los circuitos eléctricos deseados, que comprenden la parte BEOL del procedimiento. BEOL implica crear hilos de interconexión metálicos que se aíslan mediante capas dieléctricas. El material aislante era tradicionalmente una forma de vidrio de silicato, SiO2, aunque pueden utilizarse otros materiales con constante dieléctrica baja.

Los hilos de interconexión metálicos comprenden con frecuencia aluminio. En un enfoque de conexión mediante hilos denominado aluminio sustractivo, se depositan películas de cobertura de aluminio, se estructuran y se graban para formar los hilos. A continuación se deposita un material dieléctrico sobre los hilos expuestos. Las diversas capas metálicas se interconectan mediante la creación mediante ataque de perforaciones, denominados pasos, en el material aislante y depositando tungsteno en las perforaciones. Este enfoque todavía se utiliza en la fabricación de chips de memoria tales como DRAM ya que el número de niveles de interconexión es pequeño.

Más recientemente, a medida que el número de niveles de interconexión ha aumentado debido al gran número de transistores que hay que interconectar ahora en un microprocesador moderno, el tiempo dedicado a la conexión mediante hilos se ha vuelto significativo, lo que ha impulsado un cambio en el material de conexión mediante hilos de aluminio a cobre y de dióxidos de silicio a material de K baja más nuevos. El resultado es no sólo un rendimiento mejorado sino un coste reducido así como que se sustituye la tecnología de aluminio sustractivo por un procesamiento damasceno, eliminándose de ese modo varias etapas. En el procesamiento damasceno, el material dieléctrico se deposita como película de cobertura, que después se estructura y se graba dejando perforaciones o zanjas. En el procesamiento damasceno simple, se deposita entonces cobre en las perforaciones o zanjas rodeadas por una película de barrera delgada, dando como resultado pasos rellenos o líneas de hilo. En la tecnología damascena doble, tanto la zanja como el paso se fabrican antes de la deposición de cobre, dando como resultado la formación tanto de pasos como de líneas de hilo simultáneamente, lo que reduce adicionalmente el número de etapas de procesamiento. La película de barrera delgada, denominada simiente de barrera de cobre (CBS) , es necesaria para impedir la difusión de cobre en el dieléctrico. La película de barrera ideal es lo más delgada posible. Dado que la presencia de una película de barrera excesiva compite con la sección transversal de hilo de cobre disponible, la formación de la barrera continua más delgada posible representa uno de los mayores retos presentes en el procesamiento de cobre en la actualidad.

A medida que aumenta el número de niveles de interconexión, se requiere una planarización de las capas previas para garantizar una superficie plana antes de la litografía posterior. Sin ello, los niveles se volverían cada vez más

sinuosos y se extenderían fuera de la profundidad de enfoque de la litografía disponible, interfiriendo con la capacidad de estructuración. CMP (chemical mechanical planarization) es un método de procesamiento para conseguir tal planarización, aunque todavía se emplea en ocasiones el ataque posterior en seco si el número de niveles de interconexión es bajo.

El procedimiento anterior, aunque se ha descrito específicamente con respecto a la fabricación de chips de silicio, es bastante genérico para la mayoría de tipos de circuitos impresos, placas de circuito impreso, antenas, células solares, películas delgadas solares, semiconductores y similares. Como puede observarse, el procedimiento es sustractivo; es decir se deposita un metal, habitualmente cobre, de manera uniforme sobre una superficie de sustrato y después se elimina el metal no deseado, es decir, el metal que no comprende alguna parte del circuito final. Se conocen varios procedimientos aditivos, que resuelven algunos de los problemas asociados con el procedimiento sustractivo pero que generan sus propios problemas, de los que uno significativo implica la adherencia de una capa conductora formada al sustrato.

Se necesita un procedimiento aditivo para la fabricación de circuitos integrados que presente todas las ventajas de otros procedimientos aditivos pero que muestre propiedades de adhesión a sustratos mejoradas. La presente invención proporciona un procedimiento aditivo de este tipo.

El documento US2009269510 (A1) describe procedimientos y sistemas para aplicar dispositivos electrónicos impresos a diversos sustratos. En realizaciones específicas se proporcionan procedimientos y sistemas para proporcionar un recubrimiento de plata muy reflectante a un sustrato. Tales procedimientos incluyen utilizar un material fotocatalítico para iniciar la reducción de un complejo de plata aplicado al sustrato para proporcionar un recubrimiento de plata muy reflectante. El recubrimiento de plata puede conducir electricidad.

El documento WO 00/35259 (A2) describe un procedimiento para producir estructuras conductoras metálicas finas sobre un sustrato eléctricamente no conductor, según el cual se aplica un complejo de metal pesado eléctricamente no conductor al sustrato o se introduce en el mismo y el sustrato se somete selectivamente a radiación láser ultravioleta en la zona de las estructuras conductoras que van a producirse. Como resultado se liberan simientes de metales pesados y la zona se metaliza mediante reducción química.

El documento DE 10255520 (A1) describe la producción de tiras conductoras que comprende formar una película líquida con un líquido que presenta partículas eléctricamente conductoras sobre las superficies superiores de un circuito portador con un chip semiconductor o un componente electrónico con un chip semiconductor, estructurar la película por la acción de un aporte de energía local y formar una estructura de tira conductora compuesta por partículas eléctricamente conductoras sobre las superficies superiores, eliminar la película líquida que queda de las superficies para dejar la estructura de tira conductora y templar la estructura de tira conductora para unir las partículas conductoras formando tiras conductoras.

El documento US 2006143898 A1 describe un procedimiento para fabricar de manera sencilla y poco costosa una antena para una etiqueta RFID formando la antena mediante la utilización de imanes con un dibujo correspondiente a una forma de la antena. El procedimiento incluye a) colocar un sustrato... [Seguir leyendo]

Reivindicaciones:

1. Procedimiento para formar una capa conductora sobre una superficie, que comprende realizar las siguientes etapas en orden: 5 activar por lo menos una parte de una superficie del sustrato no conductora;

aplicar un campo magnético a la superficie; depositar un complejo de coordinación metálico sobre por lo menos una parte de la parte activada de la superficie;

retirar el campo magnético;

exponer el complejo de coordinación metálico a una radiación electromagnética; reducir el complejo de coordinación metálico a un metal elemental; eliminar el complejo de coordinación metálico no reducido de la superficie; secar la superficie; y depositar un material conductor sobre la superficie.

2. Procedimiento según la reivindicación 1, en el que activar la superficie del sustrato comprende grabar la superficie.

3. Procedimiento según la reivindicación 2, en el que grabar la superficie comprende uno de entre: a) un grabado químico, b) un grabado químico que comprende un ataque con un ácido, ataque con una base o ataque oxidativo, c) un grabado mecánico, d) un grabado con plasma, e) un ataque láser, y f) un ataque con plasma o láser que comprende grabar en un dibujo predeterminado.

4. Procedimiento según la reivindicación 1, en el que el campo magnético presenta una densidad de flujo magnético de por lo menos 1000 gauss.

5. Procedimiento según la reivindicación 4, en el que el campo magnético es ortogonal a la superficie.

6. Procedimiento según la reivindicación 1, en el que depositar un complejo de coordinación metálico sobre por lo menos una parte de la superficie comprende utilizar una máscara.

7. Procedimiento según la reivindicación 6, en el que la máscara comprende un circuito electrónico, en el que el circuito electrónico puede ser uno de entre un circuito analógico, un circuito digital, un circuito de señal mixta y un circuito RF.

8. Procedimiento según la reivindicación 1, en el que exponer el complejo de coordinación metálico a radiación

electromagnética comprende una radiación de microondas, radiación infrarroja, radiación con luz visible, radiación ultravioleta, radiación con rayos X o radiación gamma.

9. Procedimiento según la reivindicación 1, en el que reducir el complejo de coordinación metálico a un metal con estado de oxidación cero comprende utilizar una combinación de metales o catalizadores, o tanto metales como catalizadores.

10. Procedimiento según la reivindicación 1, en el que eliminar el complejo de coordinación metálico no reducido de la superficie comprende lavar la superficie con un disolvente.

11. Procedimiento según la reivindicación 1, en el que secar la superficie comprende uno de entre:

a) secar a temperatura ambiental o secar a temperatura elevada, y b) secar la superficie a temperatura ambiental o elevada utilizando una cámara de vacío.

12. Procedimiento según la reivindicación 1, en el que depositar un material conductor sobre la superficie comprende uno de entre:

a) una deposición electrolítica de un metal sobre la parte de la superficie que comprende el complejo de coordinación metálico reducido, y b) una deposición electrolítica de un metal sobre la parte de la superficie que comprende el complejo de coordinación metálico reducido mediante las etapas siguientes:

poner en contacto un terminal negativo de una alimentación de corriente continua con por lo menos la parte de 15 la superficie que comprende el complejo de coordinación metálico reducido;

proporcionar una disolución acuosa que comprende una sal del metal que va a depositarse, un electrodo realizado en el metal sumergido en la disolución acuosa o una combinación de los mismos;

poner en contacto un terminal positivo de la alimentación de corriente continua con la disolución acuosa;

poner en contacto por lo menos la parte de la superficie que comprende el complejo de coordinación metálico reducido con la disolución acuosa; y encender la alimentación.

13. Procedimiento según la reivindicación 1, en el que depositar un material conductor sobre la superficie comprende uno de entre:

a) una deposición no electrolítica de un metal sobre la parte de la superficie que comprende el complejo de coordinación metálico reducido, y b) una deposición no electrolítica de un metal sobre la parte de la superficie que comprende el complejo de coordinación metálico reducido que comprende poner en contacto por lo menos la parte de la superficie que 35 comprende el complejo de coordinación metálico con una disolución que comprende una sal del metal, un agente complejante y un agente reductor.

14. Procedimiento según la reivindicación 1, en el que depositar un material conductor sobre la superficie comprende la deposición de una sustancia conductora no metálica sobre la parte de la superficie que comprende el complejo de 40 coordinación metálico reducido.

15. Procedimiento según la reivindicación 14, en el que el material conductor no metálico se deposita sobre la parte de la superficie que comprende el complejo de coordinación metálico reducido mediante dispersión electrostática.

16. Procedimiento según la reivindicación 1, en el que se activa toda la superficie del sustrato no conductora y el complejo de coordinación metálico se deposita sobre toda la superficie o sobre una parte de la superficie activada.

Patentes similares o relacionadas:

Sustrato de pastilla embebida con taladro posterior, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un dispositivo, que comprende: un sustrato que tiene un primer lado y un segundo lado opuesto, en el que el sustrato es un sustrato central que […]

Estructura y procedimiento para una TSV con alivio de tensión, del 17 de Junio de 2020, de QUALCOMM INCORPORATED: Una pastilla semiconductora que comprende: un sustrato que tiene una cara activa; capas conductoras acopladas a la cara activa; una vía […]

Esquemas de interconexión posterior a la pasivación en la parte superior de los chips IC, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Una estructura de interconexión posterior a la pasivación, que comprende:

uno o más circuitos internos que comprenden uno o más dispositivos activos formados en […]

Esquemas de interconexión posterior a la pasivación en la parte superior de los chips IC, del 26 de Junio de 2019, de QUALCOMM INCORPORATED: Una estructura de interconexión posterior a la pasivación, que comprende:

uno o más circuitos internos que comprenden uno o más dispositivos activos formados en […]

Sistema multicapas con elementos de contacto y procedimiento para la creación de un elemento de contacto para un sistema multicapas, del 2 de Mayo de 2018, de INTERPANE ENTWICKLUNGS- UND BERATUNGSGESELLSCHAFT MBH & CO. KG: Sistema de capas con elemento de contacto , que comprende un sustrato , un sistema multicapas dispuesto sobre el sustrato con al menos una capa superior […]

Dispositivo para el posicionamiento y la puesta en contacto de contactos de prueba, del 22 de Noviembre de 2017, de Pac Tech - Packaging Technologies GmbH: Dispositivo para el posicionamiento y la puesta en contacto de contactos de prueba en un soporte de contactos para producir una disposición de contactos […]

Proceso para rellenar surcos de contacto en microelectrónica, del 23 de Agosto de 2017, de MacDermid Enthone Inc: Proceso para metalizar un elemento de surco de contacto a través de silicio en un dispositivo de circuito integrado semiconductor, comprendiendo […]

Estructura de interconexión basada en nanotubos de carbono redirigidos, del 11 de Febrero de 2015, de COMMISSARIAT A L'ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES: Dispositivo electrónico que comprende conexiones eléctricas que se extienden según al menos dos direcciones distintas, estando dichas conexiones realizadas por medio […]

Proceso para mejorar la adhesión de materiales poliméricos a superficies de metal, del 4 de Septiembre de 2019, de MacDermid Acumen, Inc: Una composición para promover la adhesión útil en el tratamiento de superficies de metal antes de unir materiales poliméricos a las superficies de metal, comprendiendo […]