Medición de la corriente de salida de un circuito amplificador.

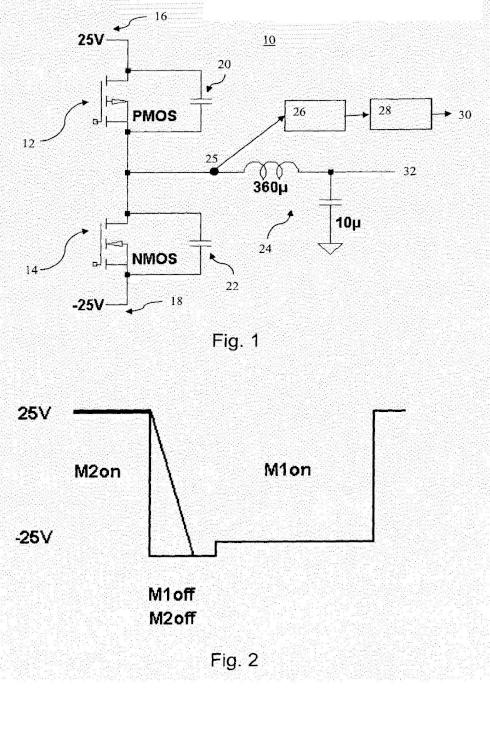

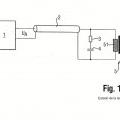

Circuito amplificador (10) con

- un primero y un segundo elemento de conmutación (12,

14), que están conectados en serie entre un primero y un segundo potencial de la tensión (16, 18) y se pueden activar de forma sincronizada en el modo de amplificador, estado conectado un elemento capacitivo (20, 22) en paralelo a al menos uno de los dos elementos de conmutación,

- con un circuito de medición (26) para la medición de los flancos de conmutación que aparecen durante la conexión de los elementos de conmutación, y

- con un circuito de medición de la corriente (28) para la determinación de la corriente de salida (30) con la ayuda de los flancos de conmutación medidos.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E12006937.

Solicitante: Airbus DS GmbH.

Inventor/es: RAPP,UDO.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03F3/217 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03F AMPLIFICADORES (medidas, ensayos G01R; amplificadores ópticos paramétricos G02F; circuitos con tubos de emisión secundaria H01J 43/30; másers, lásers H01S; amplificadores dinamoeléctricos H02K; control de la amplificación H03G; dispositivos para el acoplamiento independientes de la naturaleza del amplificador, divisores de tensión H03H; amplificadores destinados únicamente al tratamiento de impulsos H03K; circuitos repetidores en las líneas de transmisión H04B 3/36, H04B 3/58; aplicaciones de amplificadores de voz a las comunicaciones telefónicas H04M 1/60, H04M 3/40). › H03F 3/00 Amplificadores que tienen como elementos de amplificación solamente tubos de descarga o solamente dispositivos de semiconductores. › Amplificadores de potencia de clase D; Amplificadores de conmutación.

PDF original: ES-2539364_T3.pdf

Fragmento de la descripción:

Medición de la corriente de salida de un circuito amplificador La invención se refiere a un circuito amplificador de acuerdo con la reivindicación 1.

Para la alimentación de corriente de un accionamiento eléctrico se emplean amplificadores de clase-D sincronizados. Tales amplificadores son activados, en general, por medio de modulación de la amplitud del impulso (PWM) y proporcionan la mayoría de las veces a través de un filtro-LC una corriente de salida eléctrica para la alimentación de un accionamiento eléctrico. Las ventajas de los amplificadores de clase-D sincronizados consisten sobre todo en su alto rendimiento y las pérdidas reducidas de calor.

La medición de la corriente de salida, por ejemplo, para la regulación o control de un accionamiento eléctrico se puede realizar a través de una resistencia de derivación o un transformador con regulador analógico siguiente. Tales conceptos de circuito poseen, sin embargo, una flexibilidad reducida, puesto que deben estar adaptados a determinadas zonas de medición. Por ejemplo, debe seleccionarse una resistencia de derivación de acuerdo con la zona de la corriente a medir. Además, estos conceptos de circuito conducen a un gasto elevado de circuito y de compensación.

En lugar de un regulador analógico se puede emplear también un convertidor analógico-digital, que puede medir, por ejemplo a través de un multiplexor los canales de la corriente de varios amplificadores. No obstante, un concepto de este tipo condiciona de la misma manera un gasto de circuito alto, que es desfavorable en determinados campos de aplicación como por ejemplo en la navegación espacial, puesto que aquí solamente está disponible una selección reducida de componentes cualificados.

Un cometido de la presente invención consiste ahora en indicar un circuito amplificador, que posibilita una medición de su corriente de salida con un gasto de circuito lo más reducido posible.

Este cometido se soluciona por medio de un circuito amplificador con las características de la reivindicación 1. Otras configuraciones de la invención son objeto de las reivindicaciones dependientes.

Una idea en la que se basa la invención consiste en medir los flancos de conmutación que aparecen durante la conexión de elementos de conmutación de una fase final de un circuito amplificador, en particular de un amplificador de clase-D y con la ayuda de estas mediciones calcular la corriente de salida del circuito amplificador. Para reducir al mínimo las influencias de las tolerancias de los elementos de conmutación, que pueden ser implementados por medio de transistores, se puede conectar en paralelo al menos a uno de los elementos de conmutación un elemento capacitivo, en particular un condensador. Puesto que el flanco de conmutación de un elemento de conmutación real como de un transistor modifica su pendiente en función de la corriente de fase final o bien corriente de salida, se puede deducir a través de la medición del flanco de conmutación la corriente de salida. Un flanco de conmutación se puede determinar especialmente a través de una medición de un tiempo de retado de un flanco de la tensión ascendente o descendente. Para la implementación del circuito amplificador de acuerdo con la invención no se necesitan componentes críticos en determinados campos de aplicación como en la navegación espacial, como convertidores analógico-digitales y multiplexores.

Una forma de realización de la invención se refiere ahora a un circuito amplificador con un primero y un segundo elemento de conmutación, que están conectados en serie entre un primero y un segundo potencial de la tensión y se pueden activar de forma sincronizada en el modo de amplificador, estado conectado un elemento capacitivo en paralelo a al menos uno de los dos elementos de conmutación, con un circuito de medición para la medición de los flancos de conmutación que aparecen durante la conexión de los elementos de conmutación, y con un circuito de medición de la corriente para la determinación de la corriente de salida con la ayuda de los flancos de conmutación medidos.

El al menos un elemento capacitivo conectado en paralelo puede estar implementado a través de un condensador separado, que está dimensionado de tal forma que los flancos de conmutación que apareen durante la conexión de los elementos de conmutación caen o bien se elevan casi linealmente con un gradiente medible. En particular, el al menos un elemento capacitivo está seleccionado de tal forma que se reducen las influencias de la tolerancias de los elementos de conmutación hasta el punto de que su influencia sobre la medición es insignificantemente pequeña.

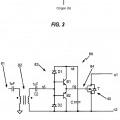

El circuito de medición puede presentar un convertidor de tiempo a digital para la medición de un periodo de tiempo de una modificación de la tensión, que aparece durante la conexión de al menos uno de los dos elementos de conmutación en el punto medio del circuito en serie de los dos elementos de conmutación. Un convertidor de tiempo a digital posibilita mediciones del intervalo de tiempo de alta exactitud, con lo que también flancos de la tensión que caen relativamente empinados pueden conducir a mediciones de tiempo útiles para los fines de la presente invención.

El circuito de medición puede estar configurado para generar una señal de inicio en el caso de que se exceda o no

se alcance una primera tensión umbral a través de la tensión en el punto medio del circuito en serie de los dos elementos de conmutación para un proceso de medición a través del convertidor de tiempo a digital y una señal de parada en el caso de que se exceda o no se alcance una segunda tensión umbral a través de la tensión en el punto medio del circuito en serie de los dos elementos de conmutación para el proceso de medición a través del convertidor de tiempo a digital. De esta manera se puede medir el flanco de conmutación de la tensión en el punto medio del circuito en serie de los dos elementos de conmutación sobre una zona determinada de la tensión, de manera que se pueden eliminar en gran medida posibles errores de medición, por ejemplo, en virtud de una tensión de alimentación oscilante del circuito amplificador. Por ejemplo, en el caso de una tensión de alimentación de +25 voltios a -25 voltios a través de la primera y la segunda tensión umbral se puede definir una zona de medición entre + 5 voltios y -5 voltios, de manera que las oscilaciones de la tensión de alimentación no tienen tampoco ninguna influencia medible sobre las mediciones.

Es posible que la primera y la segunda tensión umbral sean seleccionadas casi idénticas, de manera que sólo existe un umbral para la generación de la señal de inicio y de la señal de parada para el proceso de medición a través del convertidor de tiempo a digital, lo que puede conducir, en efecto, a una exactitud algo reducida, pero en cambio se puede implementar más fácil desde el punto de vista de la técnica de circuitos. En particular, las dos tensiones umbrales idénticas se pueden seleccionar de tal forma que se encuentran aproximadamente en el centro de la zona de la tensión de alimentación del circuito amplificador.

El circuito de medición puede presentar uno o varios comparadores para la detección de si se excede o no se alcanza la primera y/o la segunda tensión umbral a través de la tensión en el punto medio del circuito en serie de los dos elementos de conmutación y para la generación de la señal de inicio y/o señal de parada para el convertidor de tiempo a digital. Los comparadores poseen la ventaja de que disponen de especificaciones correspondientes también para los campos de aplicación críticos del circuito amplificador como la navegación espacial. Para cada tensión umbral puede estar previsto un comparador propio. En el caso de que la primera y la segunda tensión umbral sean seleccionadas idénticas, es suficiente un único comparador, lo que conduce a un gasto técnico de circuito más reducido durante la implementación del circuito amplificador.

El convertidor de tiempo a digital puede estar implementado por un módulo programable, en particular en FPGA (Field Programable Gate Array) (Campo de matriz de puertas programables) , un ASIC (Application Specific Integrated Circuit) (Circuito integrado específico de la aplicación) o un módulo convertidor de tiempo a digital especial.

El circuito de cálculo de la corriente puede estar configurado para calcular la corriente de salida con flancos de conmutación medidos, en particular el periodo de tiempo medido de la modificación de la tensión, que aparece en el caso de conexión de al menos uno de los dos elementos de conmutación, en el punto medio del circuito en serie de los dos elementos de conmutación,... [Seguir leyendo]

Reivindicaciones:

1. Circuito amplificador (10) con -un primero y un segundo elemento de conmutación (12, 14) , que están conectados en serie entre un primero y un segundo potencial de la tensión (16, 18) y se pueden activar de forma sincronizada en el modo de amplificador, estado conectado un elemento capacitivo (20, 22) en paralelo a al menos uno de los dos elementos de conmutación, -con un circuito de medición (26) para la medición de los flancos de conmutación que aparecen durante la conexión de los elementos de conmutación, y -con un circuito de medición de la corriente (28) para la determinación de la corriente de salida (30) con la ayuda de los flancos de conmutación medidos.

2. Circuito amplificador de acuerdo con la reivindicación 1, caracterizado porque el circuito de medición presenta un convertidor de tiempo a digital (34) para la medición de un periodo de tiempo de una modificación de la tensión (25) , que aparece durante la conexión de al menos uno de los dos elementos de conmutación en el punto medio del circuito en serie de los dos elementos de conmutación.

3. Circuito amplificador de acuerdo con la reivindicación 2, caracterizado porque el circuito de medición está configurado para generar una señal de inicio (36) en el caso de que se exceda o no se alcance una primera tensión umbral (38) a través de la tensión (25) en el punto medio del circuito en serie de los dos elementos de conmutación para un proceso de medición a través del convertidor de tiempo a digital y una señal de parada (40) en el caso de que se exceda o no se alcance una segunda tensión umbral (42) a través de la tensión (25) en el punto medio del circuito en serie de los dos elementos de conmutación para el proceso de medición a través del convertidor de tiempo a digital.

4. Circuito amplificador de acuerdo con la reivindicación 3, caracterizado porque la primera y la segunda tensión umbral son seleccionadas casi idénticas, y en particular las dos tensiones umbrales casi idénticas están seleccionadas de tal forma que se encuentran aproximadamente en el centro de la zona de la tensión de alimentación del circuito amplificador.

5. Circuito amplificador de acuerdo con la reivindicación 3 ó 4, caracterizado porque circuito de medición presenta uno o varios comparadores (44, 46) para la detección de si se excede o no se alcanza la primera y/o la segunda tensión umbral a través de la tensión (25) en el punto medio del circuito en serie de los dos elementos de conmutación y para la generación de la señal de inicio y/o señal de parada para el convertidor de tiempo a digital.

6. Circuito amplificador de acuerdo con la reivindicación 2, 3 ó 4, caracterizado porque el convertidor de tiempo a digital está implementado por un módulo programable, en particular en FPGA, un ASIC o un módulo convertidor de tiempo a digital especial.

7. Circuito amplificador de acuerdo con una de las reivindicaciones anteriores, caracterizado porque el circuito de cálculo de la corriente está configurado para calcular la corriente de salida con flancos de conmutación medidos, en particular el periodo de tiempo medido de la modificación de la tensión (25) , que aparece en el caso de conexión de al menos uno de los dos elementos de conmutación, en el punto medio del circuito en serie de los dos elementos de conmutación, y de la magnitud conocida del al menos un elemento capacitivo.

8. Circuito amplificador de acuerdo con la reivindicación 7, caracterizado porque el circuito de cálculo de la corriente está configurado para calcular una corriente de salida positiva o bien una corriente de salida negativa con la ayuda del periodo de tiempo medido durante un flanco de conmutación positivo y del periodo de tiempo medido durante un flanco de conmutación negativo.

9. Circuito amplificador de acuerdo con la reivindicación 8, caracterizado porque el circuito de cálculo de la corriente puede estar configurado para calcular la diferencia entre el periodo de tiempo medido durante un flanco de conmutación positivo y el periodo de tiempo medido durante un flanco de conmutación negativo y para realizar una calibración de los flancos de conmutación medidos con la ayuda de la diferencia calculada.

10. Circuito amplificador de acuerdo con una de las reivindicaciones anteriores, caracterizado porque el circuito de cálculo de la corriente está configurado para tener en cuenta valores de calibración (44) durante el cálculo de la corriente de salida con la ayuda de los flancos de conmutación medidos, los cuales han sido calculados durante mediciones de calibración en condiciones de funcionamiento conocidas del circuito amplificador, en particular durante un funcionamiento sincronizados del amplificador con una relación de exploración predeterminada, como por ejemplo 50:50 para la generación de una corriente de salida conocida.

11. Circuito amplificador de acuerdo con una de las reivindicaciones anteriores, caracterizado porque el primero y el 9

segundo potencial de la tensión pueden ser aproximadamente iguales en cuanto al importe y pueden presentar polaridades diferentes.

12. Circuito amplificador de acuerdo con una de las reivindicaciones anteriores, caracterizado porque el primer elemento de conmutación es un p-Kanal-MOSFET y el segundo elemento de conmutación es un n-Kanal-MOSFET.

13. Circuito amplificador de acuerdo con una de las reivindicaciones anteriores, caracterizado porque es parte de un circuito amplificador de clase-D y el primero y el segundo elementos de conmutación pueden ser activados con una señal modulada en la amplitud del impulso.

14. Circuito amplificador de acuerdo con una de las reivindicaciones anteriores, caracterizado porque el al menos un elemento capacitivo (20, 22) presentada un miembro de amortiguación para la limitación de la corriente, en el que 10 el miembro de amortiguación presenta especialmente un circuito paralelo de un diodo y una resistencia y está conectado entre una conexión del elemento capacitivo y una conexión de uno de los dos elementos de conmutación.

Patentes similares o relacionadas:

Interpolador de borde digitalmente controlado (DCEI) para convertidores digital-tiempo (DTC), del 22 de Noviembre de 2018, de INTEL CORPORATION: Un convertidor digital-tiempo, DTC, , que comprende: un segmento de retardo/fase gruesa que genera una señal de retardo/fase gruesa, la señal […]

Ahorro de corriente mediante código de modulación reducido y activación mediante puertas selectiva de memorias temporales de señal de RF, del 1 de Julio de 2015, de TELEFONAKTIEBOLAGET L M ERICSSON (PUBL): Un método de reducción del consumo de potencia en un amplificador de potencia de transmisor de comunicación inalámbrico, que comprende: proporcionar una señal […]

Codificación de forma de onda para aplicaciones inalámbricas, del 15 de Abril de 2015, de QUALCOMM INCORPORATED: Un aparato (102, 104, 204, 204B) para el procesamiento de datos, que comprende: medios para recibir datos codificados en forma de onda desde un dispositivo […]

Aparato y procedimiento para implementar un amplificador de accionamiento diferencial y una disposición de bobinas, del 14 de Enero de 2015, de QUALCOMM INCORPORATED: Un aparato , que comprende: una primera bobina (140a) que comprende una configuración de espiral plana, aumentando sustancialmente […]

Amplificador de potencia, del 19 de Noviembre de 2014, de Etal Group AB: Amplificador de potencia para amplificar una señal de entrada eléctrica en un rango de frecuencias de funcionamiento y proporcionar una señal de salida, […]

Modulador de alta tensión con transformador, del 13 de Agosto de 2014, de Ampegon AG: Dispositivo de alimentación de alta tensión, que comprende

- un modulador de alta tensión con una pluralidad de etapas de conmutación […]

Modulador de alta tensión con transformador, del 13 de Agosto de 2014, de Ampegon AG: Dispositivo de alimentación de alta tensión, que comprende

- un modulador de alta tensión con una pluralidad de etapas de conmutación […]

Aparato y procedimiento de implementación de un amplificador de excitación diferencial y una disposición de bobinas, del 6 de Agosto de 2014, de QUALCOMM INCORPORATED: Un aparato para reducir el ruido de salida de un amplificador, que comprende:

un único dispositivo conmutador con un estado conductivo, […]

Aparato y procedimiento de implementación de un amplificador de excitación diferencial y una disposición de bobinas, del 6 de Agosto de 2014, de QUALCOMM INCORPORATED: Un aparato para reducir el ruido de salida de un amplificador, que comprende:

un único dispositivo conmutador con un estado conductivo, […]

AMPLIFICACIÓN DE POTENCIA EN MODO CONMUTADO, del 14 de Febrero de 2012, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Método de amplificación de una señal de radiofrecuencia que comprende las etapas de: recibir una señal de envolvente (E), combinar aritméticamente una […]