Procedimiento de enmascaramiento del paso al fin de la vida útil de un dispositivo electrónico y dispositivo que comprende un módulo de control correspondiente.

Procedimiento de enmascaramiento del paso al fin de la vida útil de un dispositivo electrónico que comprende un microprocesador,

una memoria viva, una memoria muerta, una memoria no volátil reprogramable que contiene una variable de estado del fin de la vida útil del dispositivo electrónico gestionada por un módulo de control y un puerto de entrada / salida, comprendiendo el citado procedimiento las etapas siguientes:

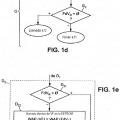

- cargar (A) en la memoria viva, a partir de la citada memoria no volátil, el valor (FdVE) de la citada variable de estado del fin de la vida útil; y, previamente a la ejecución de cualquier orden común por el citado microprocesador;

- verificar (B) el valor de la citada variable de estado del fin de la vida útil memorizada en la memoria viva (FdVR); y, en caso de valor vacío: ejecutar (C) las operaciones de paso al fin de la vida útil del dispositivo electrónico; si no, teniendo la citada variable de estado del fin de la vida útil memorizada en la memoria viva (FdVR) un valor no vacío;

- continuar (D) la inicialización y/o la ejecución de la orden común (COM) por parte del microprocesador del dispositivo electrónico; y, cuando se detecta (E) un ataque de intromisión;

- proceder a una escritura (F), en la única memoria viva, la citada variable de estado del fin de la vida útil del dispositivo electrónico (FdVR) y continuar la inicialización y/o la ejecución de la orden común; caracterizado por que el procedimiento comprende la etapa siguiente:

- proceder (G) a un borrado único de la variable de estado del fin de la vida útil (FdVE) en la citada memoria no volátil de manera diferida para efectuarlo en lugar de una próxima operación de actualización en la memoria no volátil

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/FR2012/050069.

Solicitante: MORPHO.

Nacionalidad solicitante: Francia.

Dirección: 11 Boulevard Gallieni 92130 Issy-les-Moulineaux FRANCIA.

Inventor/es: BERTHIER,MAEL, BARTHE,MICHAEL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F21/55 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 21/00 Disposiciones de seguridad para la protección de computadores, sus componentes, programas o datos contra actividades no autorizadas. › La detección de intrusiones locales o la aplicación de contramedidas.

- G06F21/75 G06F 21/00 […] › mediante la inhibición de la circuitería de análisis o operación, p. ej.:, para contrarrestar la ingeniería inversa.

PDF original: ES-2513665_T3.pdf

Fragmento de la descripción:

Procedimiento de enmascaramiento del paso al fin de la vida útil de un dispositivo electrónico y dispositivo que comprende un módulo de control correspondiente

La Invención se refiere a un procedimiento de enmascaramiento del paso al fin de la vida útil de un dispositivo electrónico, que comprende un puerto de entrada / salida, un microprocesador, una memoria viva, una memoria muerta y una memoria no volátil reprogramable que contiene una variable de estado del fin de la vida útil del dispositivo electrónico gestionada mediante un módulo de control.

Tales dispositivo electrónicos corresponden, de manera no exclusiva, a las tarjetas electrónicas, o a cualquier dispositivo electrónico que comprenda al menos o que esté en relación con, una tarjeta electrónica, tal como, particularmente, una tarjeta con microprocesadores, para la cual se requiere una buena resistencia de seguridad, frente a cualquier intromisión externa.

Para asegurar una buena resistencia de seguridad de las tarjetas citadas anteriormente, se activa un mecanismo de paso al fin de la vida útil, mediante la detección de un cierto número de errores críticos.

El proceso de paso al fin de la vida útil de este tipo de dispositivo, particularmente en lo que se refiere a las tarjetas con microprocesadores, resulta sin embargo problemático, puesto que tal proceso se apoya convencionalmente sobre un proceso de escritura en la memoria reprogramable no volátil, generalmente una memoria EEPROM, teniendo por objeto este proceso de escritura la modificación de los datos y el bloqueo de las aplicaciones.

Tal proceso resulta no obstante vulnerable, puesto que es detectable desde fuera de la tarjeta, por razones principalmente del fuerte consumo de corriente generado por el proceso de escritura en la memoria reprogramable.

Alguien deshonesto tiene por consiguiente toda la libertad para impedir la ejecución de tal proceso, cortando la alimentación eléctrica del dispositivo o de la tarjeta.

Para mejorar esta situación, se ha propuesto en los documentos FR 7 8242 y PCT/FR28/5216, hacer el proceso de paso al fin de la vida útil de tal dispositivo electrónico un hecho en un periodo de tiempo aleatorio después de que se produzca el evento, error crítico, en el origen del desencadenamiento del paso al fin de la vida útil, enmascarando, principalmente a cualquier tercera persona, la operación de escritura en memoria no volátil correspondiente al paso al fin de la vida útil, lo que impide en la práctica cualquier ataque por canal oculto.

De acuerdo con esta técnica, el enmascaramiento de cualquier escritura de una variable del estado del paso al fin de la vida útil en la memoria no volátil de un dispositivo electrónico se obtiene por dilución de esta operación de escritura en el desarrollo normal del programa de aplicación ejecutado por el dispositivo electrónico.

En la práctica, la operación de escritura de una variable en la memoria no volátil está siempre constituida por dos fases sucesivas: una fase de borrado, que lleva a la variable a tomar un valor vacío (por "valor vacío", se entiende un valor por defecto predefinido y sobre el cual un usuario de la memoria no volátil no tiene influencia, tal como "", "FF" u otro), y después una fase de operación propiamente dicha, en el curso de la cual un valor no vacío (es decir, un valor distinto del valor vacío) es aplicado a la variable en el espacio que le está dedicado en el seno de la memoria no volátil. La escritura de una variable de estado del paso al fin de la vida útil en la memoria no volátil de un dispositivo electrónico, tal como se ha previsto en la técnica anterior mencionada anteriormente, no escapa a esta regla.

Pues bien, cada una de las fases de borrado y de escritura que constituyen la operación de escritura de una variable en la memoria no volátil necesita un cierto tiempo de tratamiento y genera un cierto consumo eléctrico, aproximadamente similar en los dos casos.

A la vista de esta técnica anterior, un objeto de la presente invención es mejorar los rendimientos, manteniendo el nivel de seguridad aportado por el enmascaramiento del paso al fin de la vida útil.

Para ello, la invención propone un procedimiento de enmascaramiento del paso al fin de la vida útil de un dispositivo electrónico que comprende un microprocesador, una memoria viva, una memoria muerta, una memoria no volátil reprogramable que contiene una variable de estado del paso al fin de la vida útil del dispositivo electrónico gestionada por un módulo de control y un puerto de entrada / salida. Este procedimiento comprende las etapas siguientes:

cargar en la memoria viva, a partir de la citada memoria no volátil, el valor de la citada variable de estado del fin de la vida útil; y, previamente a la ejecución de cualquier orden común para el citado microprocesador:

verificar el valor de la citada variable de estado del fin de la vida útil memorizada en la memoria viva; y, en caso de valor vacío (es decir, un valor por defecto predefinido para la memoria no volátil): ejecutar las operaciones de paso al fin de la vida útil del dispositivo electrónico; si no, la

citada variable de estado del fin de la vida útil memorizada en la memoria viva que tiene un valor no vacío (es decir, un valor distinto del valor vacío):

continuar la inicialización y/o la ejecución de la orden común por parte del microprocesador del dispositivo electrónico; y, cuando se detecta un ataque de intromisión:

proceder a una escritura, en la única memoria viva, de la citada variable de estado del fin de la vida útil del dispositivo electrónico y continuar la inicialización y/o la ejecución de la orden común; y

proceder a un borrado único de la variable de estado del fin de la vida útil en la citada memoria no volátil de manera diferida para efectuarlo en lugar de una próxima operación de actualización (borrado y/o escritura) en la memoria no volátil.

El hecho de diferir la actualización de la variable de estado del fin de la vida útil en la citada memoria no volátil permite un enmascaramiento eficaz del paso al fin de la vida útil del dispositivo electrónico, puesto que una persona deshonesta no es capaz de distinguir la solicitación de corriente generada por esta actualización de la variable de estado del fin de la vida útil de la generada por el microprocesador del dispositivo electrónico. Se obtiene así un nivel de seguridad del mismo orden que en los documentos FR 7 8242 y PCT/FR28/5216.

Además, el hecho de proceder a un "borrado único", es decir a una fase de borrado no seguida por una fase de escritura, de la variable de estado del fin de la vida útil permite limitar el tiempo de tratamiento y el consumo eléctrico necesarios, por ejemplo, en un factor de aproximadamente 2. Los rendimientos durante la ejecución de un programa de aplicación por parte del dispositivo electrónico son así enormemente mejorados.

De acuerdo con modos de realización ventajosos que pueden ser combinados de cualquier manera que se pueda idear, el procedimiento puede además presentar todas o parte de las características que siguen.

Para un conjunto de órdenes ejecutadas por el microprocesador del dispositivo electrónico que incluye órdenes que comprenden una operación sistemática en la memoria no volátil y órdenes que no comprenden ninguna operación en la memoria no volátil, el procedimiento puede comprender además, independientemente de la detección o de la no detección de un ataque de intromisión, ejecutar un borrado único en la memoria no volátil de una variable ficticia. Esto permite enmascarar aún más el borrado de la variable de estado del fin de la vida útil del dispositivo electrónico en la memoria no volátil, introduciendo borrados "de señuelo" con una firma eléctrica similar. Una persona deshonesta puede así de manera aún más difícil identificar el borrado de la variable de estado del fin de la vida útil, a partir sólo de la solicitación de corriente que genera.

El borrado único en la memoria no volátil de la variable ficticia puede ser ejecutado en una misma página de la memoria que la de la variable de estado del fin de la vida útil.

El borrado único en la memoria no volátil de la variable ficticia puede ser ejecutado previamente a cualquier ejecución de operación de transmisión de datos sobre la línea del puerto de entrada / salida del dispositivo electrónico.

Consecutivamente a cualquier borrado único en la memoria no volátil de la variable de estado del fin de la vida útil, una etapa que consiste en verificar si es un valor vacío el valor de la variable de estado del fin de la vida útil, y, si se verifica este valor vacío, una etapa... [Seguir leyendo]

Reivindicaciones:

1. Procedimiento de enmascaramiento del paso al fin de la vida útil de un dispositivo electrónico que comprende un microprocesador, una memoria viva, una memoria muerta, una memoria no volátil reprogramable que contiene una variable de estado del fin de la vida útil del dispositivo electrónico gestionada por un módulo de control y un puerto de entrada / salida, comprendiendo el citado procedimiento las etapas siguientes:

cargar (A) en la memoria viva, a partir de la citada memoria no volátil, el valor (FdVE) de la citada variable de estado del fin de la vida útil; y, previamente a la ejecución de cualquier orden común por el citado microprocesador;

verificar (B) el valor de la citada variable de estado del fin de la vida útil memorizada en la memoria viva (FdVR); y, en caso de valor vacío: ejecutar (C) las operaciones de paso al fin de la vida útil del dispositivo electrónico; si no, teniendo la citada variable de estado del fin de la vida útil memorizada en la memoria viva (FdVR) un valor no vacío;

continuar (D) la inicialización y/o la ejecución de la orden común (COM) por parte del microprocesador del dispositivo electrónico; y, cuando se detecta (E) un ataque de intromisión;

proceder a una escritura (F), en la única memoria viva, la citada variable de estado del fin de la vida útil del dispositivo electrónico (FdVR) y continuar la inicialización y/o la ejecución de la orden común;

caracterizado por que el procedimiento comprende la etapa siguiente:

proceder (G) a un borrado único de la variable de estado del fin de la vida útil (FúN/e) en la citada memoria no volátil de manera diferida para efectuarlo en lugar de una próxima operación de actualización en la memoria no volátil.

2. Procedimiento de acuerdo con la reivindicación 1, en el que para_un conjunto de órdenes ejecutadas por el

microprocesador del dispositivo electrónico (COM G {COMW, COMt*. }) que_incluye órdenes (COMw) que

comprenden una operación sistemática en la memoria no volátil y órdenes (CM w ) que no comprenden ninguna operación en la memoria no volátil, el citado procedimiento comprende además, independientemente de la detección o de la no detección de un ataque de intromisión, la ejecución de un borrado único en la memoria no volátil de una variable ficticia, distinta de la variable de estado del fin de la vida útil del dispositivo electrónico.

3. Procedimiento de acuerdo con la reivindicación 2, en el cual el borrado único de la variable ficticia es ejecutado en una misma página de memoria que la de la citada variable de estado del fin de la vida útil.

4. Procedimiento de acuerdo con una de las reivindicaciones 2 ó 3, en el cual el borrado único en la memoria no volátil de la variable ficticia es ejecutado previamente a cualquier ejecución de operación de transmisión de datos sobre la línea del puerto de entrada / salida del dispositivo electrónico con microprocesadores.

5. Procedimiento de acuerdo con la reivindicación 4, en el cual, cuando se verifica que el valor de la citada variable de estado del fin de la vida útil (FdVR) es un valor vacío, en el citado borrado único en la memoria no volátil de la variable ficticia es sustituido un borrado único en la memoria no volátil del valor de la variable de estado del fin de la vida útil (FdVE).

6. Procedimiento de acuerdo con una de las reivindicaciones 2 a 5, que incluye además, a continuación de cualquier borrado único en la memoria no volátil de la variable de estado del fin de la vida útil (FdVE), una etapa que consiste en verificar el valor vacío, el valor de la citada variable de estado del fin de la vida útil, memorizada en la memoria viva (FdVR) y, si se verifica un valor vacío, una etapa de ejecución de las operaciones de paso al fin de la vida útil del dispositivo electrónico.

7. Procedimiento de acuerdo con una de las reivindicaciones precedentes, en el cual, mediante detección de un error de ejecución temporal de una instrucción distinta de un ataque de intromisión que no justifica un paso al fin de la vida útil del dispositivo electrónico, el citado procedimiento incluye además:

la actualización por incrementación de un contador de errores en la memoria viva;

la comparación del valor de conteo de errores con un valor de umbral; y si se sobrepasa el citado valor de umbral por parte del citado valor de conteo de errores:

la escritura en la memoria viva del valor de la citada variable de estado del fin de la vida útil del dispositivo electrónico.

8. Dispositivo electrónico que comprende un microprocesador, una memoria viva, una memoria muerta, una memoria no volátil reprogramable, que contiene una variable de estado del fin de la vida útil del dispositivo electrónico (FóVe) gestionada por un módulo de control y un puerto de entrada / salida, en el cual el citado módulo de control incluye un módulo de programa de ordenador (SCM) de ejecución de las etapas del procedimiento de acuerdo con una de las reivindicaciones 1 a 7.

9. Producto de programa de ordenador memorizado sobre un soporte de memorización y que incluye una serie de instrucciones ejecutables por un ordenador o mediante el microprocesador de un dispositivo electrónico, en el cual, durante la ejecución de las citadas instrucciones, el citado programa ejecuta las etapas del procedimiento de acuerdo con una de las reivindicaciones 1 a 7.

Patentes similares o relacionadas:

Método y aparato de procesamiento de servicio, del 3 de Junio de 2020, de Advanced New Technologies Co., Ltd: Un método para el procesamiento de servicios, el método que comprende: después de recibir una solicitud de procesamiento de servicios de un usuario, […]

Método y aparato para reconocer el comportamiento de riesgo, del 8 de Abril de 2020, de Alibaba Group Holding Limited: Un método para identificar comportamientos de riesgo dentro de una red informática, el método que comprende: adquirir datos de comportamiento del usuario, […]

Sistemas y métodos para rastrear comportamiento malicioso a través de múltiples entidades de software, del 25 de Marzo de 2020, de Bitdefender IPR Management Ltd: Un sistema de servidor que comprende al menos un procesador de hardware y una unidad de memoria, configurado el al menos un procesador de hardware para ejecutar un gestor […]

Sistemas y métodos para rastrear comportamiento malicioso a través de múltiples entidades de software, del 25 de Marzo de 2020, de Bitdefender IPR Management Ltd: Un sistema de servidor que comprende al menos un procesador de hardware y una unidad de memoria, configurado el al menos un procesador de hardware para ejecutar un gestor […]

Sistemas y métodos de seguridad informática que utilizan excepciones de introspección asíncronas, del 18 de Marzo de 2020, de Bitdefender IPR Management Ltd: Sistema anfitrión que comprende un procesador de hardware y una memoria, estando configurado el procesador de hardware para ejecutar una entidad objetivo, un analizador de […]

Sistema y método para proporcionar un nodo de almacenamiento seguro conectado a la red aérea, del 18 de Marzo de 2020, de THE BOEING COMPANY: Un sistema de almacenamiento conectado a la red, que comprende: al menos un medio de almacenamiento extraíble, el al menos un medio de […]

Servidor de seguridad de soporte lógico, del 19 de Febrero de 2020, de Idemia Identity & Security France: Procedimiento de verificación de ejecución de applets (AA1, AB1) desarrolladas en un lenguaje orientado objeto y compiladas en código intermedio, siendo el procedimiento […]

Método, aparato y sistema para detectar condiciones de seguridad de un terminal, del 5 de Febrero de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un aparato para detectar un estado de seguridad del terminal, en donde el aparato está ubicado en una unión entre una red privada y una red pública, […]

Detección y alerta de ataques cibernéticos a redes centradas en recursos, del 29 de Enero de 2020, de Palantir Technologies, Inc: Un sistema informático configurado para generar una alerta relacionada con un ataque cibernético contra un recurso, comprendiendo el sistema informático:

[…]

Detección y alerta de ataques cibernéticos a redes centradas en recursos, del 29 de Enero de 2020, de Palantir Technologies, Inc: Un sistema informático configurado para generar una alerta relacionada con un ataque cibernético contra un recurso, comprendiendo el sistema informático:

[…]