Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme.

Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo de habilitación de líneas de palabra acoplado a la línea de palabra para poner en estado activo la línea de palabra;

un amplificador de detección acoplado al par de líneas de bit para detectar niveles de voltaje en el par de líneas de bit y restaurar una carga en la celda de memoria;

un circuito de ecualización de líneas de bit acoplado al par de líneas de bit para precargar el par de líneas de bit; y caracterizada por que la DRAM incluye

un circuito de temporización para recibir una señal de control y controlar el circuito de ecualización de líneas de bit, el dispositivo de habilitación de líneas de palabra, y el amplificador de detección;

en la que,

en un primer flanco de la señal de control, el dispositivo de habilitación de líneas de palabra se desactiva, el amplificador de detección se desactiva, y el circuito de ecualización de líneas de bits se activa;

después de un primer retardo desde el primer flanco de la señal de control, el circuito de ecualización de líneas de bits se desactiva y el dispositivo de habilitación de líneas de palabra se activa;

después del primer retardo más un segundo retardo desde el primer flanco de la señal de control, el amplificador de detección se activa; y

en un segundo flanco de la señal de control, el dispositivo de habilitación de líneas de palabra se desactiva, el amplificador de detección se desactiva, y el circuito de ecualización de líneas de bits se activa.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E10175918.

Solicitante: Conversant Intellectual Property Management Inc.

Nacionalidad solicitante: Canadá.

Dirección: 11 Hines Road, Suite 203 Ottawa, ON K2K 2X1 CANADA.

Inventor/es: DEMONE,PAUL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C11/406 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 11/00 Memorias digitales caracterizadas por la utilización de elementos de almacenamiento eléctricos o magnéticos particulares; Elementos de almacenamiento correspondientes (G11C 14/00 - G11C 21/00 tienen prioridad). › Organización o control de los ciclos de de refresco o de regeneración de la carga.

- G11C11/4076 G11C 11/00 […] › Circuitos de sincronización (para la gestión de la regeneración G11C 11/406).

- G11C7/10 G11C […] › G11C 7/00 Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Disposiciones de interfaz para entrada/salida [I/O] de datos, p. ej. circuitos de control de entrada/salida [I/O] de datos, memorias intermedias de entrada/salida [I/O] de datos.

- G11C7/22 G11C 7/00 […] › Circuitos de sincronización o de reloj para la lectura-escritura [R-W]; Generadores o gestión de señales de control para la lectura-escritura [R-W].

- G11C8/18 G11C […] › G11C 8/00 Disposiciones para seleccionar una dirección en una memoria digital (circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193). › Circuitos de sincronización o de reloj; Generación o gestión de señales de control de dirección, p. ej. para las señales de selección de dirección de línea [RAS] o de selección de dirección de columna [CAS].

PDF original: ES-2516791_T3.pdf

Fragmento de la descripción:

Arquitectura de DRAM de alta velocidad con una latencia de acceso uniforme

La presente invención se refiere en general a arquitecturas de DRAM de alta velocidad, y específicamente a la temporización de operaciones de lectura, escritura y refresco.

Antecedentes de la invención

Tradicionalmente, el diseño de productos básicos genéricos de dispositivos de Memoria Dinámica de Acceso Aleatorio (DRAM) se ha centrado más en lograr un coste-por-bit bajo a través de una alta densidad de bits acumulada que en lograr un mayor rendimiento de la memoria. El motivo de esto es que la capacidad de las celdas de una matriz de memoria bidimensional se incrementa cuadráticamente con el escalado, mientras que el área de tara de los amplificadores de detección de líneas de bit, los controladores de líneas de palabra, y los decodificadores de direcciones de fila (o direcciones x) y direcciones de columna (o direcciones y) se incrementa linealmente con el escalado.

Por lo tanto, el hecho de que el diseño haya puesto énfasis en la densidad de las memorias ha dado como resultado el diseño de DRAMs básicas genéricas que tienen submatrices del mayor tamaño posible en la práctica, a pesar de su efecto fuertemente perjudicial sobre el tiempo necesario para llevar a cabo la lectura de celdas, la detección de líneas de bit, la restauración de celdas y la ecualización y precarga de líneas de bit. Como consecuencia, el rendimiento relativamente bajo de arquitecturas de DRAM tradicionales, en comparación con la Memoria Estática de Acceso Aleatorio (SRAM), ha limitado en general su uso a aplicaciones de gran capacidad, alta densidad y sensibles al coste, donde el rendimiento es un factor secundario.

Además, las arquitecturas tradicionales de DRAM minimizan el número de pines de señales en los dispositivos de memoria mediante el multiplexado de líneas de dirección entre los componentes de fila y columna de la dirección. Como consecuencia, el carácter bidimensional de la organización de las matrices de DRAM ha sido siempre una parte inherente de la interfaz entre el control o la lógica de la memoria y los dispositivos de memoria de DRAM.

La llegada de tecnologías de DRAM de interfaz síncrona, tales como la SDRAM, la RAMBUS directa, y la SDRAM de velocidad de datos doble (DDR), ha sustituido las señales de control independiente de filas y columnas de las tecnologías de DRAM de interfaz asincrona, tales como el modo de paginación rápida (FPM) y la salida de datos extendida (EDO), por órdenes codificadas.

No obstante, la organización tradicional de direccionamiento lógico bidimensional de arquitecturas previas se ha

mantenido.

Uno de los primeros intentos de incrementar el rendimiento de la DRAM minimizando el impacto de la latencia y del tiempo de ciclo de las lentas operaciones de acceso a filas debido al uso de grandes matrices de celdas, condujo a la creación de dos clases diferentes de operaciones de memoria, siendo los dos bien conocidas en la industria. Una primera clase comprende accesos a bancos. Un acceso a banco consta de una orden de abrir fila seguida por un acceso a columna. En referencia a la figura 1 a, se ilustra un diagrama de temporización para un acceso a banco. Una segunda clase comprende accesos a página. Un acceso a página consta de un acceso de columna a una fila que se ha dejado abierta por medio de una orden previa de abertura de fila o de acceso de banco. Como consecuencia, los accesos de página son típicamente más rápidos que los accesos de banco. En referencia a la figura 1b, se ilustra un diagrama de temporización para un acceso de página. La eficacia de los accesos de página en la reducción de la latencia media es debida a la localización espacial estadística en los patrones de acceso de memoria de muchas aplicaciones informáticas y de comunicaciones. Es decir, existe una gran probabilidad de que accesos de memoria consecutivos apunten a la misma fila.

Una mejora adicional de la precisión de dicho esquema de clase dual de acceso a memoria es la creación de arquitecturas de DRAM que dividen explícitamente cada dispositivo de memoria en dos o más regiones del mismo tamaño a las que se hace referencia como bancos. La intención de esta mejora arquitectónica es reducir parcialmente la tara de los accesos de fila permitiendo el solapamiento de accesos de memoria en un banco, mientras que el otro banco se ocupa de una operación de abertura o cierre de fila.

Un sistema que implementa una arquitectura de múltiples bancos es bien conocido en la industria y se ilustra de forma general en la figura 2a por medio del número de referencia 200. En la figura 2b se ilustra un diagrama de temporización para un sistema del tipo mencionado.

Un problema fundamental con todos estos esquemas es la retención del sistema de dos clases de accesos a memoria para compensar parcialmente el lento acceso de fila asociado a las grandes matrices de DRAM. Muchas aplicaciones de tiempo real, tales como los procesadores de señal digital, quedan limitadas por el rendimiento de la memoria en el peor de los casos. Estos sistemas no pueden tolerar diferencias en la temporización de los accesos a memoria en función de los patrones de dirección particulares de accesos consecutivos. Incluso los diseños de

macrobloques de la DRAM embebida con rendimiento optimizado tienden a mantener el paradigma de la clase dual de acceso de las arquitecturas de DRAM básicas genéricas.

En referencia a la figura 3a, con el número referencia 300 se ilustra de manera general un intento adicional de incrementar el rendimiento de la DRAM con el uso de una arquitectura de puerto dual. La arquitectura con puerto dual es un avance más reciente en la arquitectura de DRAM para lograr un rendimiento mayor. Cada celda de memoria MC está conectada a dos líneas de bit, BL1 y BL2, a través, respectivamente, de transistores de acceso N1 y N2. Esta arquitectura de celdas permite un acceso simultáneo de la celda de memoria MC a través de un transistor de acceso y su línea de bit asociada, por ejemplo N1 y BL1, mientras que BL2, asociada al otro transistor de acceso N2, experimenta una precarga y una ecualización. Como consecuencia, puede producirse un segundo acceso por medio de N2 sin ningún retardo en la línea de bit BL2 de precarga.

Alternando de un lado a otro entre los dos transistores de acceso y sus líneas de bit respectivas, esta arquitectura puede ocultar completamente la tara asociada al cierre de filas y a la precarga y la ecualización de las líneas de bit. No obstante, el principal inconveniente de este sistema es la alta reducción de la densidad de bits dentro de la matriz de DRAM debido al doblamiento del número de transistores de acceso y de líneas de bit por celda de memoria, en comparación con los diseños convencionales de DRAM. Además, un sistema de este tipo usa también una arquitectura de líneas de bit abiertas lo cual no es deseable debido a su susceptibilidad al acoplamiento de ruido desadaptado con respecto a pares de líneas de bit.

El documento US 6072743 da a conocer circuitos para controlar la temporización interna de operaciones de memoria en un dispositivo de DRAM. El documento US 5808959 da a conocer circuitos similares para una memoria de SRAM.

Sumario de la invención

La presente invención proporciona un aparato y métodos para acceder a una memoria DRAM que presenta las funcionalidades que se exponen en las reivindicaciones adjuntas.

Breve descripción de los dibujos

A continuación se describirán, a título de ejemplo, unas formas de realización de la presente invención, únicamente haciendo referencia a los dibujos siguientes, en los cuales:

la figura 1a es un diagrama de temporización para un acceso a bancos de memoria;

la figura 1b es un diagrama de temporización para un acceso a páginas de memoria;

la figura 2a es un diagrama de bloques simplificado que ilustra una arquitectura de una memoria con múltiples

bancos (técnica anterior);

la figura 2b es un diagrama de temporización para el sistema ilustrado en la figura 2a;

la figura 3a es un diagrama esquemático de una arquitectura de memoria de puerto dual (técnica anterior);

la figura 3b es un diagrama de temporización que ilustra operaciones de lectura y escritura para la arquitectura de puerto dual ilustrada en la figura 3 a;

la figura 4 es un gráfico que compara una celda de DRAM convencional (técnica anterior) con una celda de DRAM de acuerdo con una forma de realización de la presente invención;

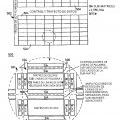

la figura 5 es un diagrama de bloques de una arquitectura de memoria general de acuerdo con una forma de realización de la presente invención;

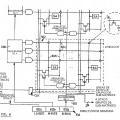

la figura 6 es un esquema conceptual... [Seguir leyendo]

Reivindicaciones:

1. Memoria Dinámica de Acceso Aleatorio (DRAM) que comprende:

una celda de memoria acoplada a un par de líneas de bit y a una línea de palabra;

un dispositivo de habilitación de líneas de palabra acoplado a la línea de palabra para poner en estado activo la línea de palabra;

un amplificador de detección acoplado al par de líneas de bit para detectar niveles de voltaje en el par de líneas de bit y restaurar una carga en la celda de memoria;

un circuito de ecualización de líneas de bit acoplado al par de líneas de bit para precargar el par de líneas de bit; y caracterizada por que la DRAM incluye

un circuito de temporización para recibir una señal de control y controlar el circuito de ecualización de líneas de bit, el dispositivo de habilitación de líneas de palabra, y el amplificador de detección;

en la que,

en un primer flanco de la señal de control, el dispositivo de habilitación de líneas de palabra se desactiva, el amplificador de detección se desactiva, y el circuito de ecualización de líneas de bits se activa;

después de un primer retardo desde el primer flanco de la señal de control, el circuito de ecualización de líneas de bits se desactiva y el dispositivo de habilitación de líneas de palabra se activa;

después del primer retardo más un segundo retardo desde el primer flanco de la señal de control, el amplificador de detección se activa; y

en un segundo flanco de la señal de control, el dispositivo de habilitación de líneas de palabra se desactiva, el amplificador de detección se desactiva, y el circuito de ecualización de líneas de bits se activa.

2. DRAM según la reivindicación 1, en la que, en el primer flanco de la señal de control, el dispositivo de habilitación de líneas de palabra se desactiva y el circuito de ecualización de líneas de bit se activa.

3. DRAM según la reivindicación 2, que comprende además:

un par de dispositivos de acceso a columnas acoplados al par de líneas de bit; un par de buses de datos acoplado al par de dispositivos de acceso a columnas; en la que,

después del primer retardo más el segundo retardo más un tercer retardo desde el primer flanco de la señal de control, el par de dispositivos de acceso a columnas se activa.

4. DRAM según la reivindicación 3, que comprende además:

un circuito de ecualización de buses de datos acoplado al par de buses de datos para precargar el par de buses de datos;

en la que,

después del primer retardo más el segundo retardo más el tercer retardo más un cuarto retardo desde el primer flanco de la señal de control, el par de dispositivos de acceso a columnas se desactiva, el circuito de ecualización de buses de datos se activa, preferentemente en el segundo flanco de la señal de control, el circuito de ecualización de buses de datos se desactiva; y que incluye opclonalmente

un biestable acoplado al par de buses de datos para retener datos del par de buses de datos;

en la que,

en el segundo flanco de la señal de control, el biestable se activa por Impulsos de reloj.

5. DRAM según la reivindicación 1, en la que la señal de control es o bien una señal de reloj o bien una señal estroboscópica.

6. DRAM según la reivindicación 5, en la que el primer flanco de la señal de control y el segundo flanco de la señal de control presentan la misma polaridad, preferentemente

el primer flanco de la señal de control y el segundo flanco de la señal de control son flancos de subida.

7. DRAM según la reivindicación 6, en la que el segundo flanco de la señal de control es el primer flanco que presenta la misma polaridad que el primer flanco de la señal de control tras el primer flanco de la señal de control, o

el segundo flanco de la señal de control es el segundo flanco que presenta la misma polaridad que el primer flanco de la señal de control tras el primer flanco de la señal de control.

8. Método de lectura de datos en una Memoria Dinámica de Acceso Aleatorio (DRAM), que comprende: recibir una orden de lectura y una dirección en un primer flanco de una señal de control;

y caracterizado por que presenta las etapas siguientes:

desactivar un dispositivo de habilitación de líneas de palabra para deselecclonar una línea de palabra en el primer flanco de la señal de control;

activar el dispositivo de habilitación de líneas de palabra para seleccionar la línea de palabra de acuerdo con la dirección después de un primer retardo desde el primer flanco de la señal de control;

activar un amplificador de detección acoplado a un par de líneas de bit para detectar datos en una celda de memoria acoplada a la línea de palabra y al par de líneas de bit después del primer retardo más un segundo retardo desde el primer flanco de la señal de control; y

desactivar el dispositivo de habilitación de líneas de palabra para deselecclonar la línea de palabra en un segundo flanco de la señal de control.

9. Método según la reivindicación 8, que comprende además:

activar un circuito de ecualización de líneas de bit y desactivar el dispositivo de habilitación de líneas de palabra en el primer flanco de la señal de control, y opcíonalmente

activar un circuito de ecualización de buses de datos acoplado a un par de buses de datos para precargar el par de buses de datos después de un tercer retardo desde el primer flanco de la señal de control.

10. Método según la reivindicación 9, que comprende además:

desactivar el circuito de ecualización de buses de datos en el primer flanco de la señal de control, y opcíonalmente

desactivar el circuito de ecualización de buses de datos en el segundo flanco de la señal de control.

11. Método según la reivindicación 10, que comprende además:

activar un par de dispositivos de acceso a columnas acoplados al par de líneas de bit y el par de buses de datos después del primer retardo más el segundo retardo más un cuarto retardo desde el primer flanco de la señal de control, y opcíonalmente

retener datos del par de buses de datos en el segundo flanco de la señal de control.

12. Método según la reivindicación 8, en el que la señal de control es o bien una señal de reloj o bien una señal estroboscóplca.

13. Método de escritura de datos en una Memoria Dinámica de Acceso Aleatorio (DRAM), que comprende:

recibir una orden de escritura, unos datos que se deben escribir, y una dirección en un primer flanco de una señal de control; y caracterizado por que presenta las etapas siguientes:

desactivar un dispositivo de habilitación de líneas de palabra para deselecclonar una línea de palabra en el primer flanco de la señal de control;

activar el dispositivo de habilitación de líneas de palabra para seleccionar la línea de palabra de acuerdo con

la dirección después de un primer retardo desde el primer flanco de la señal de control;

activar un par de dispositivos de acceso a columnas acoplados a un par de líneas de bit y un par de buses de datos después del primer retardo más un segundo retardo más un tercer retardo desde el primer flanco de la 5 señal de control;

activar una memoria Intermedia de escritura para escribir los datos que se deben escribir en el par de buses de datos después de un cuarto retardo desde el primer flanco de la señal de control; y

desactivar el dispositivo de habilitación de líneas de palabra para deseleccionar la línea de palabra en un

segundo flanco de la señal de control.

14. Método según la reivindicación 13, que comprende además:

desactivar la memoria intermedia de escritura en el segundo flanco de la señal de control, o

retener datos del par de buses de datos en el segundo flanco de la señal de control.

15. Método según la reivindicación 13, en el que la señal de control es o bien una señal de reloj o bien una señal 20 estroboscópica.

Patentes similares o relacionadas:

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Método de procesado de datos, aparato de almacenamiento, disco de estado sólido y sistema de almacenamiento, del 28 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesado de datos, aplicado a un sistema de almacenamiento, en donde el sistema de almacenamiento comprende un anfitrión, un controlador y un […]

Potencia programable para una interfaz de memoria, del 21 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el control de retardo en una interfaz de memoria, que comprende: proporcionar una polarización de voltaje a un circuito […]

Circuitos de líneas de bits globales de Memoria Estática de Acceso Aleatorio (SRAM) para reducir los fallos de energía durante los accesos de lectura de memoria, y procedimientos y sistemas relacionados, del 17 de Abril de 2019, de QUALCOMM INCORPORATED: Un circuito de línea de bits global de memoria estática de acceso aleatorio, SRAM, para una pluralidad de células de bits de SRAM, que […]

Dispositivo de memoria híbrida con una única interfaz, del 23 de Enero de 2019, de Microsoft Technology Licensing, LLC: Un procedimiento que comprende: recibir, en un controlador , órdenes, direcciones y datos en un dispositivo de memoria mediante una interfaz definida asociada […]

Dispositivo y procedimiento para el procesamiento de cuadros de datos en serie, del 11 de Octubre de 2018, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo para el procesamiento de cuadros de datos en serie, que comprende una unidad de convertidor en serie-paralelo , una unidad de evaluación […]

Arquitectura central en serie de memoria no volátil, del 3 de Septiembre de 2014, de Conversant Intellectual Property Management Inc: Sistema de memoria que comprende: banco de memoria para suministrar datos de lectura de flujo de bits en serie en respuesta a una operación […]

PROCEDIMIENTO DE REPETICIÓN PARA TARJETAS INTELIGENTES, del 28 de Diciembre de 2011, de NXP B.V.: Dispositivo de recuperación, para recuperar datos de almacenamiento válidos (SD) en la memoria que presenta: - medios de almacenamiento para almacenar datos […]