USO DEL SISTEMA DE RENOMBRADO DE REGISTROS PARA EL ENVÍO DE LOS RESULTADOS INTERMEDIOS ENTRE INSTRUCCIONES CONSTITUTIVAS DE UNA INSTRUCCIÓN EXPANDIDA.

Un procedimiento de ejecución de una instrucción expandida, que comprende:

la conversión (100) de la instrucción expandida en dos o más instrucciones constituyentes ejecutables por separado; la asignación (102) de un número de registro físico desde un almacén (22) a una primera instrucción constituyente que genera un resultado intermedio, en la que la asignación comprende además la creación de una entrada en una tabla de renombrado de instrucciones constituyentes (24) que mapea un identificador de la primera instrucción constituyente al número de registro físico; y la asociación (104) del número de registro físico asignado con una segunda instrucción constituyente que recibe el resultado intermedio, en el que la asociación comprende además la realización de una búsqueda en la tabla de renombrado de instrucciones constituyentes (24) que usa el primer identificador de instrucción constituyente; mediante lo cual dicho resultado intermedio se pasa desde la primera a la segunda instrucción constituyente por medio del registro físico identificado por dicho número de registro físico (106, 108)

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2008/051958.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: ATTN: INTERNATIONAL IP ADMINISTRATION 5775 MOREHOUSE DRIVE SAN DIEGO, CALIFORNIA 92121 ESTADOS UNIDOS DE AMERICA.

Inventor/es: DIEFFENDERFER,JAMES NORRIS, SMITH,RODNEY WAYNE, SARTORIUS,THOMAS ANDREW, MCLLVAINE,MICHAEL,SCOTT, NUNAMAKER,NATHAN,SAMUEL.

Fecha de Publicación: .

Fecha Solicitud PCT: 24 de Enero de 2008.

Clasificación Internacional de Patentes:

- G06F9/30R4

- G06F9/38D

- G06F9/38E

Clasificación PCT:

- G06F9/30 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

- G06F9/38 G06F 9/00 […] › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia.

Fragmento de la descripción:

Antecedentes

La presente invención se refiere de modo general a procesadores, y en particular a un sistema y un procedimiento para la utilización de recursos de renombrado de registros existentes para ejecutar instrucciones expandidas que pasen 5 resultados parciales.

**(Ver fórmula)**

**(Ver fórmula)**

**(Ver fórmula)**

Las instrucciones de los procesadores operan sobre datos obtenidos de, y escriben sus resultados en, la memoria. Los procesadores modernos utilizan una estructura de memoria jerárquica que comprende unos pocos elementos de memoria rápidos y caros, tales como registros, en el nivel superior. La jerarquía de la memoria comprende a continuación sucesivamente tecnologías de memoria más lentas pero más eficaces en coste a niveles más bajos, tales 10 como las memorias caché (SRAM), memoria principal de estado sólido (DRAM) y discos (medios magnéticos u ópticos), respectivamente. Para aplicaciones tales como los dispositivos electrónicos portátiles, la DRAM es a menudo el nivel más bajo en la jerarquía de memoria.

La mayoría de arquitecturas del conjunto de instrucciones (ISA) de los procesadores incluyen un conjunto de registros de finalidad general (GPR), que son registros ideados usados para pasar los datos entre instrucciones, y a y desde la 15 memoria. Las instrucciones que realizan operaciones lógicas y aritméticas sobre los datos leen sus operandos desde, y escriben sus resultados en, GPR específicos. De modo similar, las instrucciones de acceso a memoria leen los datos a ser almacenados en memoria desde los GPR y escriben los datos cargados desde la memoria a los GPR. Un compilador asigna identificadores de GPR de origen y destino a cada instrucción y ordena las instrucciones de modo que se calculen los resultados apropiados. Es decir, las instrucciones se disponen en un orden de programación que 20 garantiza los resultados correctos mandando a las instrucciones anteriores que almacenen resultados en GPR específicos y mandando a las instrucciones posteriores que lean esos GPR para obtener operandos para el procesamiento posterior. Los identificadores de GPR son etiquetas lógicas (por ejemplo, r0 - r15).

Algunos procesadores modernos soportan instrucciones “expandidas” esto es, instrucciones que realizan más de una operación aritmética o lógica. Por ejemplo, la instrucción ADD r1, r2, r3 LSL r4 implementa la ecuación r1 = r2 + (r3 << 25 [r4]), esto es, desplaza el valor del registro r3 en una cantidad almacenada en r4, añade este resultado al valor en r2 y almacena la suma en el registro r1. En un procesador cuyo sumador requiere un tiempo de ciclo completo, esta instrucción expandida se puede implementar como dos instrucciones separadas, compuestas —una instrucción de desplazamiento que desplaza a la izquierda el valor en r3, generando un resultado intermedio y una instrucción de suma que añade el resultado intermedio al valor en r2 y almacena la suma en r1—. En algunos procesadores —es decir, 30 procesadores que soportan el envío de operandos y sólo ejecutan instrucciones expandidas en el orden del programa— el paso de los resultados intermedios desde la instrucción de desplazamiento a la instrucción de suma es directo. En general, sin embargo —particularmente en procesadores superescalares que soportan la ejecución de instrucciones fuera de orden—, se deben añadir al procesador recursos adicionales, tales como registros “improvisados” y lógica de control compleja, para implementar fiablemente el envío de resultados intermedios entre las instrucciones constituyentes 35 de una instrucción expandida.

El documento US 6 279 102 describe un aparato que incluye al menos dos registros y una unidad de renombrado para asignar al menos uno de los registros físicos a un registro original.

El documento US 6 279 102 desvela además macro instrucciones decodificadas en forma de micro operaciones. Dicha decodificación introduce registros temporales como direcciones de origen o destino de las micro operaciones para el 40 almacenamiento de resultados intermedios. Smotherman M. y col., "Improving CISC instruction decoding performance using a fill unit", EE.UU., IEEE COMPUT. SOC. 29 de noviembre de 1995, págs. 219 a 229 describe las dependencias de los datos y controles.

El documento US 2003/149862 describe el renombrado de registros usando una tabla de seguimiento que tiene entradas para cada registro. 45

Sumario

De acuerdo con la invención, se proporciona: un procedimiento de acuerdo con la reivindicación 1; y un aparato de acuerdo con la reivindicación 10.

Preferentemente, el pase de resultados intermedios entre instrucciones constituyentes de una instrucción expandida se realiza usando recursos de renombrado de registro y lógica de control. Una primera instrucción constituyente genera 50 resultados intermedios y se le asigna un PRN en una tabla de renombrado de instrucciones constituyentes y escribe los resultados intermedios en el registro físico. Una segunda instrucción constituyente realiza una búsqueda en la tabla de renombrado de instrucciones constituyentes y lee los resultados intermedios del registro físico. La lógica de renombrado de instrucciones constituyentes sigue las instrucciones constituyentes a través de la línea de ejecución y borra las entradas en la tabla de renombrado de instrucciones constituyentes y devuelve el PRN a una lista de libres cuando la 55 segunda instrucción constituyente ha leído los resultados intermedios.

La instrucción expandida se puede convertir en dos o más instrucciones constituyentes ejecutables por separado. Se asigna a una primera instrucción constituyente un número de registro físico que genera un resultado intermedio. El número de registro físico asignado se asocia con una segunda instrucción constituyente que recibe el resultado intermedio.

El procesador puede incluir una o más líneas de ejecución de instrucciones operativa para ejecutar instrucciones 5 expandidas mediante la generación de una primera instrucción constituyente que genera resultados intermedios y una segunda instrucción constituyente que recibe los resultados intermedios. El procesador incluye también un almacén de registros físicos, teniendo cada uno un número de registro físico, y una tabla de renombrado de instrucciones constituyentes operativa para mapear los identificadores de instrucciones con los números de registro físicos. El procesador incluye adicionalmente una lógica de control operativa para crear una entrada en la tabla de renombrado de 10 instrucciones constituyentes para la primera instrucción constituyente y operativa además para realizar una búsqueda en la tabla de renombrado de instrucciones siguientes para la segunda instrucción constituyente. Los resultados intermedios se pasan desde la primera a la segunda instrucción constituyente por medio de los registros físicos identificados por los números de registro físicos.

Breve descripción de los dibujos 15

La Figura 1 es un diagrama de bloques funcional de un procesador que utiliza recursos de renombrado de registros para efectuar el paso de resultados intermedios entre instrucciones constituyentes de una instrucción expandida.

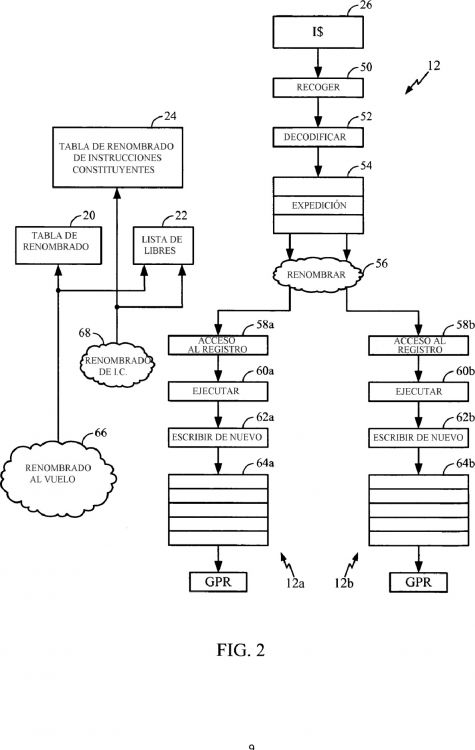

La Figura 2 es un diagrama de bloques funcional de la línea de ejecución del procesador de la Figura 1.

La Figura 3 es un diagrama de flujo de un procedimiento de ejecución de una instrucción expandida.

Descripción detallada 20

La Figura 1 representa un diagrama de bloques funcional de un procesador 10 que tiene una lógica para utilizar recursos de renombrado de registros para hacer el seguimiento del paso de los resultados intermedios entre instrucciones constituyentes generados por una instrucción expandida. El procesador 10 ejecuta instrucciones en una línea de ejecución de instrucciones 12 de acuerdo con la lógica de control 14. La línea de ejecución 12 puede ser un diseño superescalar, con múltiples líneas de ejecución inferiores paralelas 12a, 12b. La línea de ejecución 12 incluye 25 varios registros o cerrojos 16, organizados en fases de línea de ejecución, así como circuitos de cálculo y lógicos como las Unidades Lógicas y Aritméticas (ULA) (no mostradas). Un archivo de Registro de Finalidad General (GPR) 18 proporciona registros que comprenden la cima de la jerarquía de la memoria. Como se ha comentado en el presente documento, el GPR 18 puede incluir una Tabla de Renombrado (RT, “Renaming Table”) 20, una lista de...

Reivindicaciones:

1. Un procedimiento de ejecución de una instrucción expandida, que comprende:

la conversión (100) de la instrucción expandida en dos o más instrucciones constituyentes ejecutables por separado;

la asignación (102) de un número de registro físico desde un almacén (22) a una primera instrucción constituyente que 5 genera un resultado intermedio, en la que la asignación comprende además la creación de una entrada en una tabla de renombrado de instrucciones constituyentes (24) que mapea un identificador de la primera instrucción constituyente al número de registro físico; y

la asociación (104) del número de registro físico asignado con una segunda instrucción constituyente que recibe el resultado intermedio, en el que la asociación comprende además la realización de una búsqueda en la tabla de 10 renombrado de instrucciones constituyentes (24) que usa el primer identificador de instrucción constituyente;

mediante lo cual dicho resultado intermedio se pasa desde la primera a la segunda instrucción constituyente por medio del registro físico identificado por dicho número de registro físico (106, 108).

2. El procedimiento de la reivindicación 1 que comprende además la ejecución (106) de la primera instrucción constituyente para generar el resultado intermedio. 15

3. El procedimiento de la reivindicación 2 que comprende además la ejecución (108) de la segunda instrucción constituyente por lo cual el resultado intermedio se envía como operando desde la primera instrucción constituyente a la segunda instrucción constituyente.

4. El procedimiento de la reivindicación 2 que comprende además el almacenamiento (106) del resultado intermedio en un registro identificado por el número de registro físico. 20

5. El procedimiento de la reivindicación 4 que comprende además la ejecución de la segunda instrucción constituyente y la recuperación (108) del resultado intermedio desde el registro identificado por el número de registro físico.

6. El procedimiento de la reivindicación 1 en el que el número de registro físico se selecciona de una lista de registros físicos disponibles y se elimina de la lista.

7. El procedimiento de la reivindicación 1 que comprende además la liberación (110, 112) del número de registro físico 25 del almacén (22) después de que la segunda instrucción constituyente lea el resultado intermedio.

8. El procedimiento de la reivindicación 7 en el que la liberación del número de registro físico del almacén (22) comprende la adición de un número de registro físico a la lista de registros físicos disponibles.

9. El procedimiento de la reivindicación 1 en el que el almacén de registros físicos (22) es un almacén de renombrado de registros. 30

10. Un procesador (10), que comprende:

una o más líneas de ejecución de instrucciones (12) operativas para ejecutar una instrucción expandida mediante la generación de una primera instrucción constituyente que genera resultados intermedios y una segunda instrucción constituyente que recibe los resultados intermedios;

un almacén de registros físicos (22), que tiene cada uno un número de registro físico; 35

caracterizado por una tabla de renombrado de instrucciones constituyentes (24) operativa para mapear identificadores de instrucciones con los números de registros físicos; y

lógica de control operativa para crear una entrada en la tabla de renombrado de instrucciones constituyentes para la primera instrucción constituyente y operativa además para realizar una búsqueda en la tabla de renombrado de instrucciones constituyentes de la segunda instrucción constituyente, usando el identificador de la primera instrucción 40 constituyente;

por medio de lo cual los resultados intermedios se pasan desde la primera a la segunda instrucción constituyente a través de los registros físicos identificados por los números de registro físico (106, 108).

11. El procesador de la reivindicación 10 que comprende además una lista libre de números de registros físicos disponibles en el almacén (22) y en el que la lógica de control es operativa además para eliminar entradas en la tabla de 45 renombrado de instrucciones constituyentes y devolver los números de registro físico a la lista libre después de que las segundas instrucciones constituyentes reciban los resultados intermedios.

12. El procesador de la reivindicación 10 en el que el almacén de registros físicos (22) se utiliza adicionalmente para el renombrado de registros.

13. El procesador de la reivindicación 10 en el que la tabla de renombrado de instrucciones constituyentes (24) es una tabla de renombrado de registros.

Patentes similares o relacionadas:

MICROPROCESADOR CON SELECCIÓN AUTOMÁTICA DE PARALELISMO SIMD, del 9 de Junio de 2011, de QUALCOMM INCORPORATED: Un procedimiento para controlar el paralelismo de operaciones en un procesador de datos en paralelo, que comprende: monitorizar una o más condiciones […]

METODOS Y APARATO PARA LA EJECUCION MULTIPROCESO DE INSTRUCCIONES INFORMATICAS, del 9 de Diciembre de 2009, de SONY COMPUTER ENTERTAINMENT INC.: Un sistema informático multiproceso, que comprende: un procesador principal operable para gestionar el procesado de bucles de instrucciones […]

METODOS Y APARATO PARA LA EJECUCION MULTIPROCESO DE INSTRUCCIONES INFORMATICAS, del 9 de Diciembre de 2009, de SONY COMPUTER ENTERTAINMENT INC.: Un sistema informático multiproceso, que comprende: un procesador principal operable para gestionar el procesado de bucles de instrucciones […]

INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 27 de Mayo de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para borrar elementos de memorias intermedias de traducción de direcciones en un sistema informático , comprendiendo el sistema […]

INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 27 de Mayo de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para borrar elementos de memorias intermedias de traducción de direcciones en un sistema informático , comprendiendo el sistema […]

INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 29 de Abril de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de […]

INVALIDACIÓN DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 29 de Abril de 2011, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 19 de Abril de 2010, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar los elementos de tablas de traducción y borrar los correspondientes elementos de tablas de traducción dinámica de direcciones (DAT) […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 19 de Abril de 2010, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar los elementos de tablas de traducción y borrar los correspondientes elementos de tablas de traducción dinámica de direcciones (DAT) […]

Control de ejecución de hilos en un procesador multihilo, del 24 de Junio de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para controlar la ejecución de hilos en un entorno informático, comprendiendo dicho método: detener , mediante un hilo […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Predicados uniformes en sombreadores para unidades de procesamiento de gráficos, del 11 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para procesar datos, comprendiendo el procedimiento: recibir una indicación de que todos los subprocesos de una urdimbre […]