PILA DE TRANSACCIÓN PARA DISPOSITIVOS ELECTRÓNICOS QUE INCLUYEN MEMORIAS NO VOLÁTILES CON UN NÚMERO LIMITADO DE CICLOS DE ESCRITURA.

Procedimiento para implementar una pila de transacciones (2) en un dispositivo electrónico que incluye una parte de memoria no volátil con ciclo de escritura limitado (5),

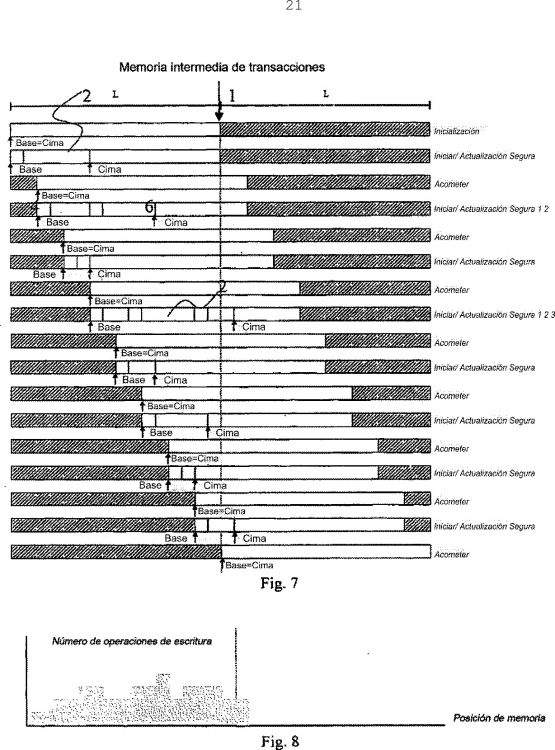

del tipo que comprende el almacenamiento de datos no volátiles durante transacciones seguras caracterizado porque proporciona una pila de transacciones (2) dinámicamente deslizante dentro de una memoria intermedia de transacciones (1) de dicha parte de memoria no volátil después de la ejecución de una de dichas transacciones seguras, teniendo dicha pila de transacciones (2) un tamaño menor que el tamaño de dicha memoria intermedia de transacciones (1), dicha pila de transacciones (2) después de la ejecución de una de dichas transacciones seguras superponiéndose parcialmente a la pila de transacciones antes de dicha ejecución de una de dichas transacciones seguras

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E05425277.

Solicitante: INCARD SA.

Nacionalidad solicitante: Suiza.

Dirección: 39 CHEMIN DU CHAMP-DES-FILLES 1228 PLAN-LES-OUATES 1204 GENEVA SUIZA.

Inventor/es: CONCILIO,MARIANO.

Fecha de Publicación: .

Fecha Solicitud PCT: 29 de Abril de 2005.

Fecha Concesión Europea: 9 de Junio de 2010.

Clasificación PCT:

- G06F1/30 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 1/00 Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76). › Medios para actuar en caso de avería o de interrupción de la alimentación (únicamente para el reinicio G06F 1/24).

- G06F1/32 G06F 1/00 […] › Medios destinados a economizar energía.

- G06F11/14 G06F […] › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Detección o corrección de errores en los datos por redundancia en las operaciones, p. ej. mediante la utilización de diversas secuencias de operaciones que conduzcan al mismo resultado (G06F 11/16 tiene prioridad).

- G06F12/02 G06F […] › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › Direccionamiento o asignación; Traslado (secuenciación de direcciones de programa G06F 9/00; disposiciones para seleccionar una dirección en una memoria digital G11C 8/00).

- G06F9/312 G06F […] › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Control de operaciones de carga, de registro o de borrado.

- G06F9/355 G06F 9/00 […] › Direccionamiento indexado.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

Campo de aplicación

La presente invención se refiere a una pila de transacciones para dispositivos electrónicos que incluyen memoria no volátil con ciclo de escritura limitado.

En particular, la invención se refiere a dispositivos del tipo anterior y que comprenden un procedimiento para almacenar datos no volátiles durante transacciones seguras, siendo dichos datos no volátiles archivos, contraseñas, claves criptográficas, certificados, perfiles de usuarios, así como variables de estado de sistema operativos, variables de estado de aplicaciones, el registro de aplicaciones, aplicaciones ejecutables, etcétera. Antecedentes de la invención

Como es bien sabido, un dispositivo incorporado como una tarjeta de circuito integrado usa una parte de memoria de semiconductor de estado sólido para almacenar datos no volátiles.

La categoría de los datos no volátiles incluye ejecutables de aplicación, archivos, contraseñas, claves criptográficas, certificados, perfiles de usuarios, así como variables de estado de sistemas operativos, variables de estado de aplicaciones, el registro de aplicaciones, etcétera. El contenido de todos los datos anteriores es variable durante la fase operativa del dispositivo pero conservarán su valor durante el apagado.

Por el contrario, el valor de los datos volátiles se pierde durante una fase de apagado y se inicializa en el arranque del dispositivo. La categoría de datos volátiles incluye la pila de la CPU, memorias intermedias para operaciones de entrada/salida, memorias intermedias para cálculos temporales, etcétera.

La memoria no volátil asegura que el valor de los datos

no volátiles no se pierde después de una desconexión regular del dispositivo, es decir, cuando se produce la desactivación eléctrica en un estado inactivo del dispositivo. Este es el caso típico, cuando la desactivación es activada por la lógica del terminal al que está conectado el dispositivo.

Por otra parte, si se produce una desactivación eléctrica accidental durante la ejecución de una aplicación, específicamente durante una operación de actualización de datos no volátiles complejos, es posible que el valor de los datos se deje en un estado inconsistente que podría comprometer, completa o parcialmente, el funcionamiento o la seguridad del dispositivo en las sesiones de encendido sucesivas.

Para enfrentarse a este problema, los sistemas operativos proporcionan el conocido mecanismo de transacción.

El mecanismo de transacción proporciona a la capa de aplicación los instrumentos para agrupar juntas un número arbitrario de operaciones de escritura, estableciendo que tienen que considerarse como una única operación de escritura atómica respecto a eventos como un apagado. La aplicación tiene que marcar todas las operaciones de escritura entre dos instrucciones. Podemos decir, en un pseudolenguaje simple, que todas las operaciones de escritura deben estar incluidas entre dos instrucciones, concretamente “IniciarTransaccion” (del inglés ”BeginTransaction”)y“AcometerTransaccion” (del inglés ”CommitTransaction”), como se muestra esquemáticamente en la Figura 1.

En caso de apagado durante la ejecución del código incluido entre dichas dos instrucciones IniciarTransaccion y AcometerTransaccion, el sistema operativo asegura que se restaura el valor de todos los datos no volátiles afectados por las “Actualizaciones seguras”, en el siguiente arranque del dispositivo, al valor que tenían antes de la sentencia IniciarTransaccion.

Las implementaciones avanzadas permiten transacciones multinivel, con niveles anidados de instrucciones IniciarTransaccion y AcometerTransaccion.

El mecanismo de transacción puede implementarse usando una pila de transacciones, como se aclarará mediante la siguiente descripción, apoyada por la Figura 2.

En esta Figura, los posibles estados de ejecución de una transacción, que comprende dos Operaciones Seguras, están indicados con 10. En particular, en la Figura 2a la transacción está en un estado “Estado inicial”, en la Figura 2b está en un estado “Comenzar transacción”, en la Figura 2c en un estado “Actualización segura”, en 2d aún está en el estado “Actualización segura” y, por último, en 2e está en un estado “Asignar transacción”.

En la Figura 2 la memoria no volátil también se muestra esquemáticamente y se indica con el número de referencia 20; sus valores, durante todos los estados posibles de ejecución de la transacción, se indican dentro de las celdas de la memoria no volátil 20. En particular, la dirección inicial de la memoria no volátil 20 en la que se escribirán datos por la primera operación segura se indica con A1 y la longitud de los datos que han de escribirse durante la primera operación segura con L1.

Igualmente, la dirección inicial de la memoria no volátil 20 en la que se escribirán datos por la segunda operación segura se indica con L2. Por último, la pila de transacciones se indica con 30, y el puntero Cima a la pila de transacciones con 40.

La pila de transacciones 30 se limpia en la invocación de IniciarTransaccion cuando la transacción está en el “Estado inicial”. Cada operación de Actualización segura, como se muestra en las Figuras 2c y 2d, añade un registro sobre la pila de transacciones 30, que contiene la información para recuperar el valor original de los datos después de un apagado inesperado potencial (típicamente: la dirección/tamaño/valor de los datos). En la invocación de AcometerTransaccion la pila de transacciones 30 se vuelve a limpiar.

La Figura 3 muestra la recuperación, en el arranque del dispositivo, de los valores de los datos originales en caso

de apagado del dispositivo durante la primera operación de Actualización segura. En particular, en la Figura 3a se muestra esquemáticamente el arranque del dispositivo después de un apagado incorrecto que causó la pérdida de algunos datos dentro de la memoria no volátil 20, indicando los datos perdidos con el símbolo “???”.

En la Figura 3b una transacción de restauración (en inglés “Rollback Transaction”) restaura los datos perdidos a su posición original, recuperando los valores correctos de la pila de transacciones 30.

La Figura 5, en cambio, ofrece un ejemplo del uso de la pila de transacciones 30 en caso de ocho transacciones consecutivas, que contienen un número diferente de operaciones de Actualización segura. Las transacciones indicadas con los números 1, 3, 5, 6, 7, 8 contienen sólo una actualización, la transacción número 2 contiene 2 actualizaciones y la transacción número 4 contiene 3 actualizaciones. La Figura 6 representa un gráfico que muestra el número total de operaciones de escritura a continuación de las ocho transacciones mostradas esquemáticamente en la figura 5.

Si la desactivación del dispositivo es regular, no hay ejecución de aplicación en curso que, en el arranque del dispositivo, la pila de transacciones 30 esté siempre vacía. Por otra parte, si el dispositivo es desactivado mientras una aplicación está funcionando y el flujo de ejecución está entre las dos instrucciones IniciarTransaccion y AcometerTransaccion, entonces el sistema operativo, en el siguiente arranque, encuentra la pila de transacciones 30 NO vacía y lleva a cabo las operaciones de recuperación según los registros en la pila de transacciones. Después de eso, se limpia la pila.

Obsérvese que la implementación de la pila de transacciones 30 necesita una variable no volátil para almacenar el puntero a la parte superior de la pila de transacciones 30 (Cima en lo que viene a continuación). Por supuesto, el valor de Cima es en sí mismo un dato sensible

respecto a un evento de apagado accidental. Por eso, se requiere un mecanismo dedicado, independiente de la pila de transacciones, para asegurar la “atomicidad” de la variable Cima. Esto se obtiene típicamente mediante una memoria intermedia circular sin punteros dedicada. Esta solución es viable porque la variable Cima es un dato único, corto y de tamaño predefinido (2 ó 4 bytes). La Figura 4 muestra un ejemplo de un mecanismo de actualización atómico para el puntero Cima, por medio de una memoria intermedia circular sin punteros de 5 franjas. Cada franja está etiquetada con un indicador binario (“0”...

Reivindicaciones:

1. Procedimiento para implementar una pila de transacciones (2) en un dispositivo electrónico que incluye una parte de memoria no volátil con ciclo de escritura limitado (5), del tipo que comprende el almacenamiento de datos no volátiles durante transacciones seguras caracterizado porque proporciona una pila de transacciones

(2) dinámicamente deslizante dentro de una memoria intermedia de transacciones (1) de dicha parte de memoria no volátil después de la ejecución de una de dichas transacciones seguras, teniendo dicha pila de transacciones (2) un tamaño menor que el tamaño de dicha memoria intermedia de transacciones (1), dicha pila de transacciones (2) después de la ejecución de una de dichas transacciones seguras superponiéndose parcialmente a la pila de transacciones antes de dicha ejecución de una de dichas transacciones seguras.

2. Procedimiento según la reivindicación 1, caracterizado por el hecho de que la parte inferior de la dirección inicial

(4) de dicha pila de transacciones (2) se recoloca en una posición nueva dentro de la memoria intermedia de transacciones (1).

3. Procedimiento según la reivindicación 1, caracterizado por el hecho de que la parte inferior de la dirección inicial

(4) de ducha pila de transacciones (2) se coloca al comienzo de dicha memoria intermedia de transacciones (1) durante la fase de inicialización de dicho dispositivo (5).

4. Procedimiento según la reivindicación 2, caracterizado por el hecho de que dicho puntero base (4) se desplaza a lo largo de dicha memoria intermedia de transacciones (1), después de una transacción de comienzo de dicha transacción segura, recolocando su dirección en una ubicación predeterminada incluida entre: -la dirección inicial de dicha memoria intermedia de

transacciones (1) y -la ubicación obtenida sumando, a dicha dirección inicial, la diferencia entre las longitudes de dicha memoria intermedia de transacciones (1) y dicha pila de transacciones (2).

5. Procedimiento según la reivindicación 3, caracterizado por el hecho de que dicho puntero base (4) se coloca en una posición específica durante la fase de inicialización de dicho dispositivo (5), según una regla de ubicación predeterminada.

6. Procedimiento según la reivindicación 2, caracterizado por el hecho de que dicho puntero base (4) se desplaza a lo largo de dicha memoria intermedia de transacciones (1) después de una transacción de comienzo de dicha transacción segura, recolocando su dirección en una ubicación aleatoria incluida entre: -la dirección inicial de dicha memoria intermedia de transacciones (1) y -la ubicación obtenida sumando, a dicha dirección inicial, la diferencia entre las longitudes de dicha memoria intermedia de transacciones (1) y dicha pila de transacciones (2).

7. Procedimiento según la reivindicación 2 caracterizado por el hecho de que dicha pila de transacciones (2) se desplaza cíclicamente a lo largo de dicha memoria intermedia de transacciones (1) por medio de la colocación de dicho puntero base (4) en diferentes posiciones a lo largo de la memoria intermedia de transacciones (1) después de cada transacción de comienzo y recolocando cíclicamente dicho puntero base (4) al comienzo de dicha memoria intermedia de transacciones (1).

8. Dispositivo electrónico que incluye una parte de memoria no volátil con ciclo de escritura limitado (5) y en

el que se almacenan datos no volátiles durante transacciones

seguras caracterizadas por una pila de transacciones (2)

dinámicamente deslizante dentro de una memoria intermedia de

transacciones (1) de dicha parte de memoria no volátil

5 después de la ejecución de una de dichas transacciones

seguras, teniendo dicha pila de transacciones (2) un tamaño

menor que el tamaño de dicha memoria intermedia de

transacciones (1), dicha pila de transacciones (2) después de

la ejecución de una de dichas transacciones seguras 10 superponiéndose parcialmente a la pila de transacciones antes

de dicha ejecución de una de dichas transacciones seguras.

Patentes similares o relacionadas:

Almacenamiento de datos gráficos comprimidos en ancho de banda, del 6 de Noviembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento, que comprende: almacenar, mediante al menos un procesador, una pluralidad de datos gráficos comprimidos en ancho de banda en una pluralidad respectiva […]

Método de procesado de datos, aparato de almacenamiento, disco de estado sólido y sistema de almacenamiento, del 28 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesado de datos, aplicado a un sistema de almacenamiento, en donde el sistema de almacenamiento comprende un anfitrión, un controlador y un […]

Gestión de memoria automática que usa una unidad de gestión de memoria, del 24 de Julio de 2019, de aicas GmbH: Método implementado por ordenador , para actuar sobre un módulo automático de gestión de memoria en un sistema informático que tiene una memoria de acceso […]

Uso de compresión de memoria para reducir la carga de compromiso de memoria, del 6 de Mayo de 2019, de Microsoft Technology Licensing, LLC: Un método de reducir una cantidad de compromiso de memoria para un programa en un dispositivo de cálculo , comprendiendo el método: determinar […]

Controlador de acceso a memoria, sistemas y procedimientos para optimizar los tiempos de acceso a memoria, del 9 de Enero de 2019, de QUALCOMM INCORPORATED: Un controlador de memoria , que comprende: un controlador configurado para acceder al menos a una ubicación de memoria correspondiente […]

Sistema de gestión de datos y método, del 30 de Noviembre de 2018, de LIFESCAN SCOTLAND LIMITED: Un sistema de gestión de datos que comprende: - una primera sección de memoria no volátil dividida en una pluralidad de ubicaciones […]

Método de obtención anticipada de datos para un sistema de almacenamiento de tabla hash distribuida DHT, nodo y sistema, del 21 de Noviembre de 2018, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de obtención anticipada de datos para un sistema de almacenamiento de tabla hash distribuida DHT que comprende un primer nodo de almacenamiento y un segundo […]

Método de gestión de la asignación de memoria flash en un token electrónico, del 27 de Diciembre de 2017, de GEMALTO SA: Un método para gestionar la asignación de memoria flash en un token electrónico (ET), disponiendo dicho token (ET) de una memoria (ME) que comprende […]